Interpreting Machines

### THE COMPUTER SCIENCE LIBRARY

### **Operating and Programming Systems Series**

PETER J. DENNING, Editor

Halstead A Laboratory Manual for Compiler

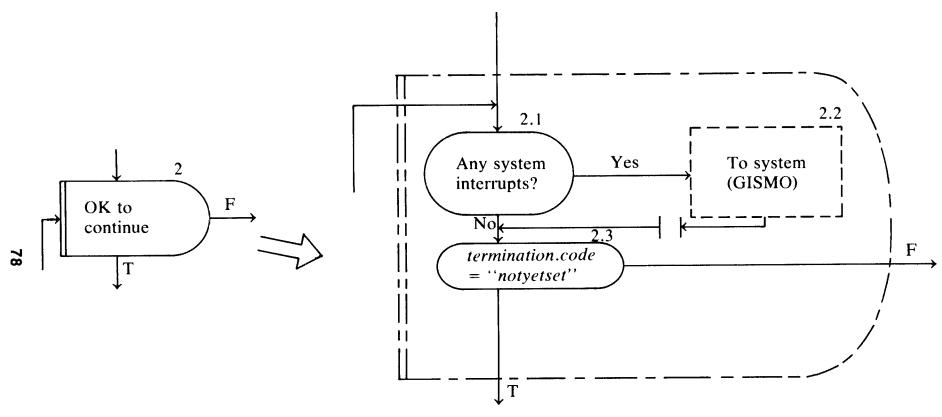

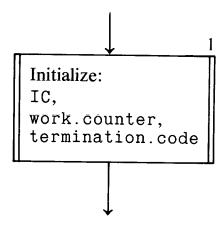

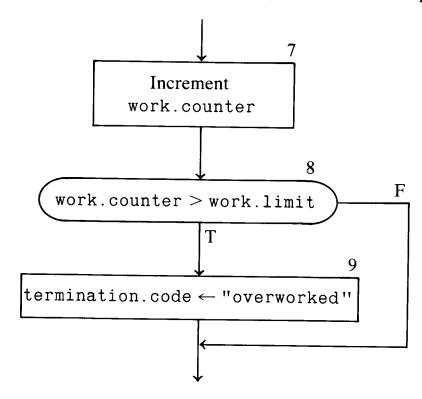

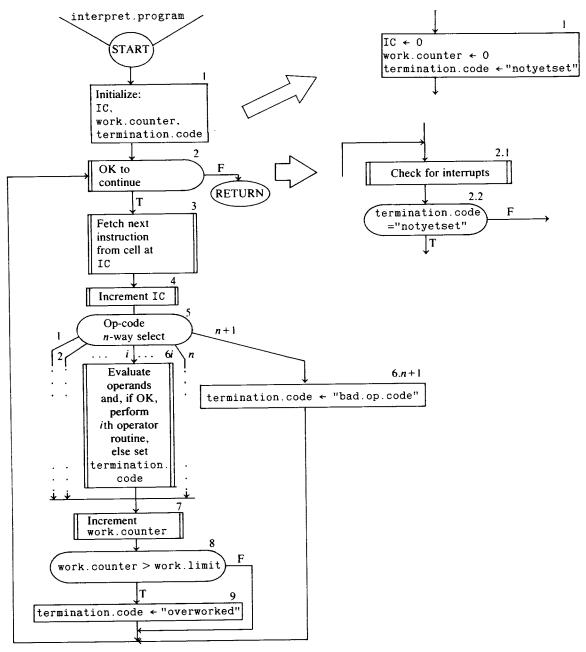

and Operating System Implementation

Spirn Program Behavior: Models and Measurements

Halstead Elements of Software Science

Franta A Process View of Simulation

Organick and Hinds Interpreting Machines: Architecture and

Programming of the B1700/B1800

Series

# Interpreting Machines: Architecture and Programming of the B1700/B1800 Series Elliott I.Organick

The University of Utah

James A. Hinds

**Burroughs Corporation**

Elsevier North-Holland, Inc. 52 Vanderbilt Avenue, New York, New York 10017

Distributors outside the United States and Canada: THOMOND BOOKS (A Division of Elsevier/North-Holland Scientific Publishers, Ltd). P. O. Box 85 Limerick, Ireland

©1978 by Elsevier North-Holland, Inc.

### Library of Congress Cataloging in Publication Data

Organick, Elliott Irving, 1925-

Interpreting Machines: Architecture and Programming of the B1700/B1800 Series.

(Operating and programming systems series) (The Computer science library) Includes index.

1. Burroughs B1726 (Computer) I. Hinds, James A., joint author. II. Title.

QA76.8.B85073 001.6'4'04 77-12127

ISBN 0-444-00241-3

ISBN 0-444-00242-1 pbk.

### **Contents**

| <b>Preface</b> |                                                     | ix |

|----------------|-----------------------------------------------------|----|

| Chapter        | 1 Universal Host Computers                          | 1  |

| 1.1            | Structure of Storage in the B1700 Family            |    |

|                | of Computers                                        | 4  |

| 1.2            | The B1726 Model of Storage                          | 7  |

| Chapter        | 2 The B1700 as an Interpreting Machine              | 10 |

| 2.1            | Instruction Decoding                                | 12 |

| Chapter        | 3 Organization of the B1726 Microprocessor          | 16 |

| 3.1            | Data Fetch and Addressing                           | 16 |

| 3.2            | Data Examination and Manipulation                   | 28 |

|                | 3.2.1 The arithmetic capability or                  |    |

|                | "Function Box"                                      | 31 |

|                | 3.2.2 Arithmetic tidbits                            | 32 |

|                | Instruction Decoding                                | 33 |

| 3.4            | Control                                             | 37 |

| Chapter        | 4 The B1700 Computation Environment                 | 42 |

|                | The Burroughs Concept of "Codefile"                 | 45 |

|                | Constructing a Computation Environment              | 46 |

| 4.3            | Implementing a Complete MIL Program                 | 47 |

| 4.4            | Declarations in MIL                                 | 50 |

| 4.5            | Literals                                            | 57 |

| 4.6            | Input/Output in the McMIL Language                  | 59 |

|                | 4.6.1 Declaring files                               | 64 |

| 4.7            | The LOADER (Details)                                | 68 |

| Chapter        | 5 The Structure of an Interpreter                   | 74 |

| 5.1            | Detection and Response to Faults and Interrupts     | 74 |

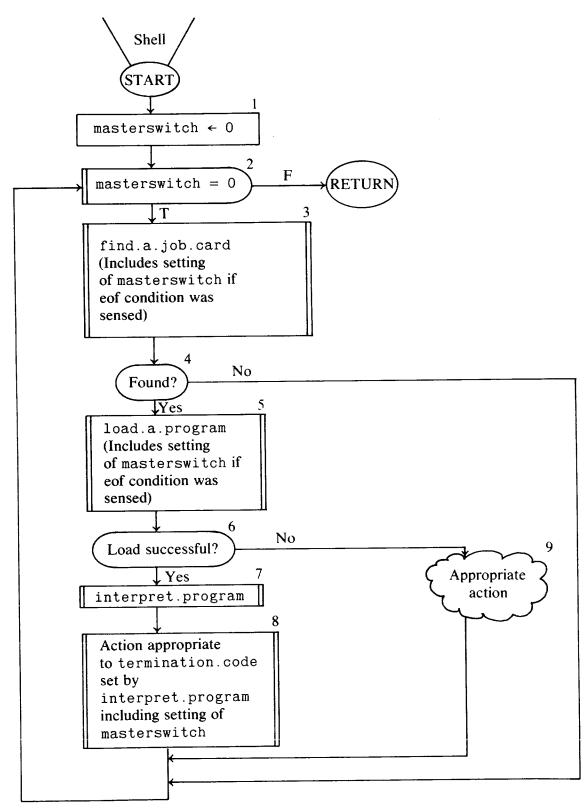

| 5.2            | The Host Environment                                | 80 |

| 5.3            | The Shell Concept                                   | 81 |

| 5.4            | Moving Top Down on the Interpreter Structure        | 87 |

|                | 5.4.1 Storage representation for the target machine | 88 |

|                | 5.4.2 Discussion of MIL code for ADD routine        | 98 |

| vi  | Contents |

|-----|----------|

| = = |          |

| Chapte | r 6 MIL Coding for Data Manipulation           | 104 |

|--------|------------------------------------------------|-----|

| 6.1    |                                                | 104 |

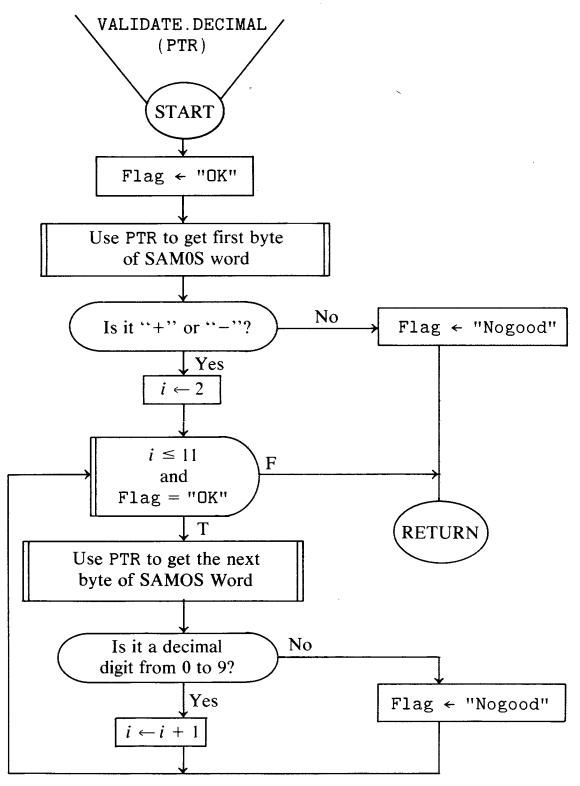

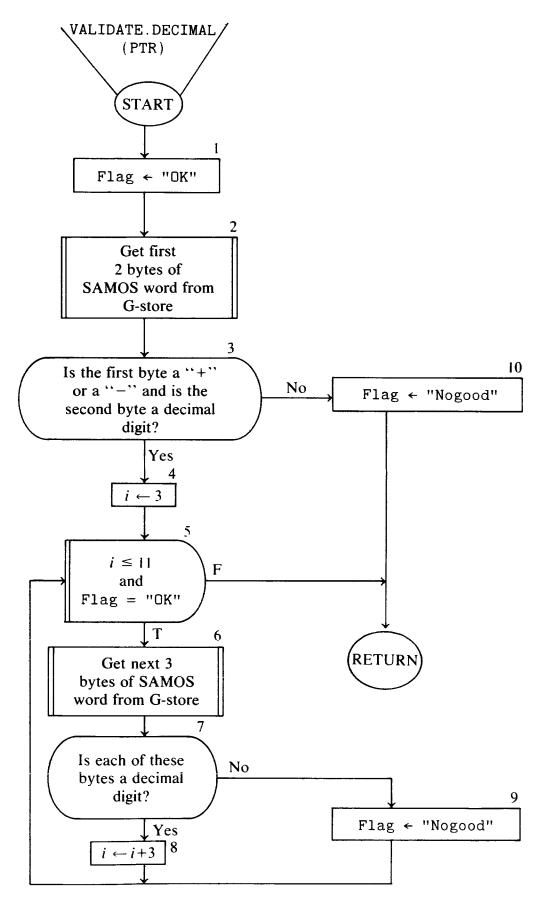

| 6.2    | VALIDATE.DECIMAL:                              |     |

|        | Case Study for a Utility Routine               | 106 |

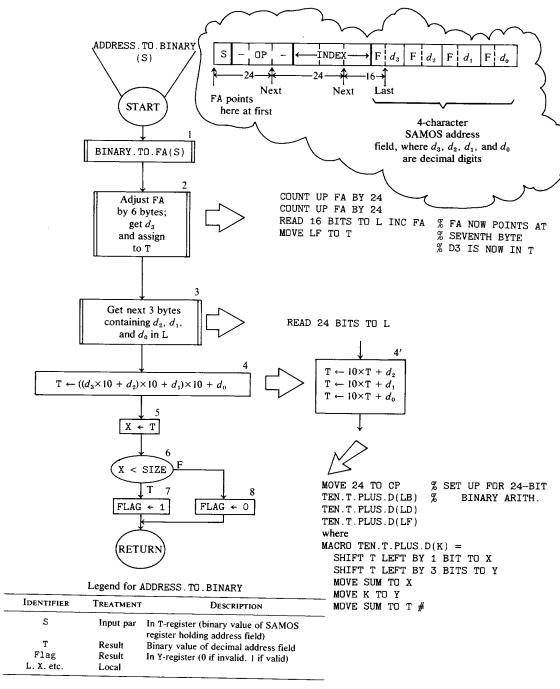

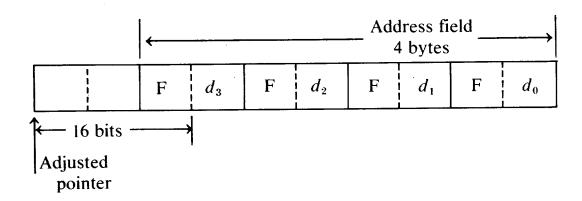

| 6.3    | BINARY.TO.FA                                   | 121 |

| 6.4    | ADDRESS.TO.BINARY                              | 124 |

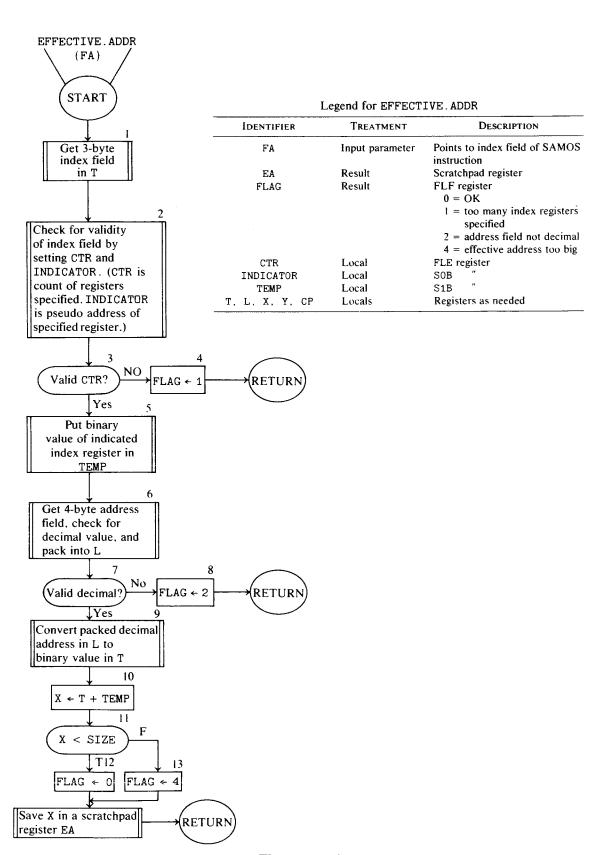

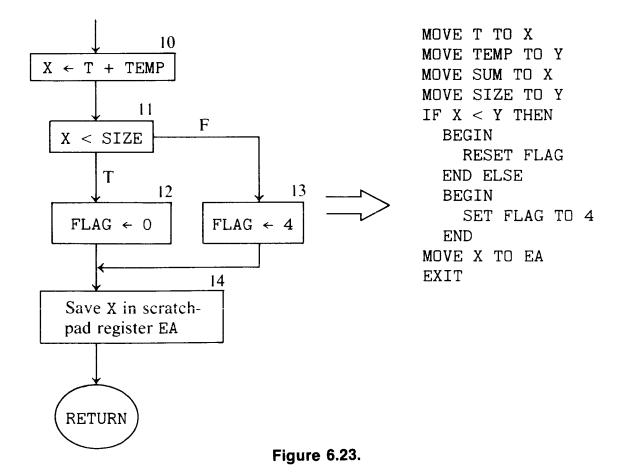

| 6.5    | EFFECTIVE.ADDRESS                              | 127 |

| 6.6    | The ADD Routine                                | 137 |

| 6.7    | UNPACK.AND.WRITE                               | 147 |

| 6.8    | Chapter Summary                                | 149 |

| Chapte | r 7 The Split-Level Control Store              | 150 |

| 7.1    |                                                | 152 |

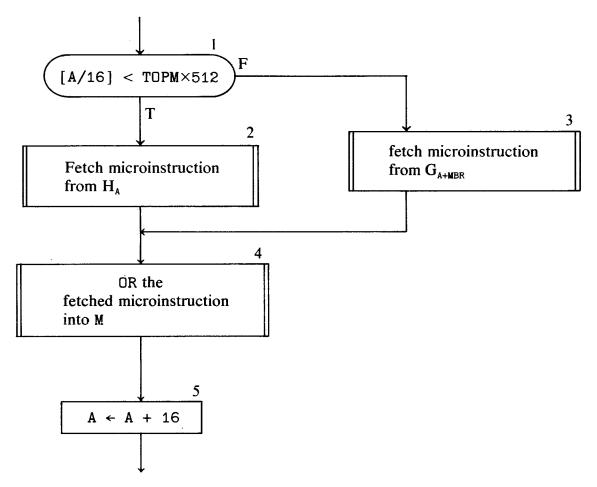

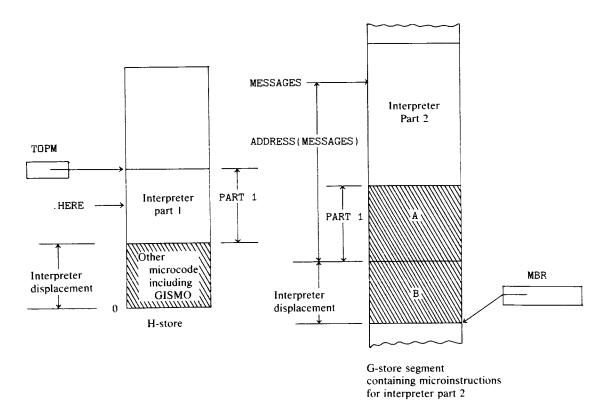

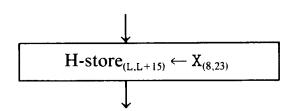

| 7.2    | Microinstruction Fetch from H-Store or G-Store | 155 |

| 7.3    | Embedding Tabulated Data in MIL Programs       | 157 |

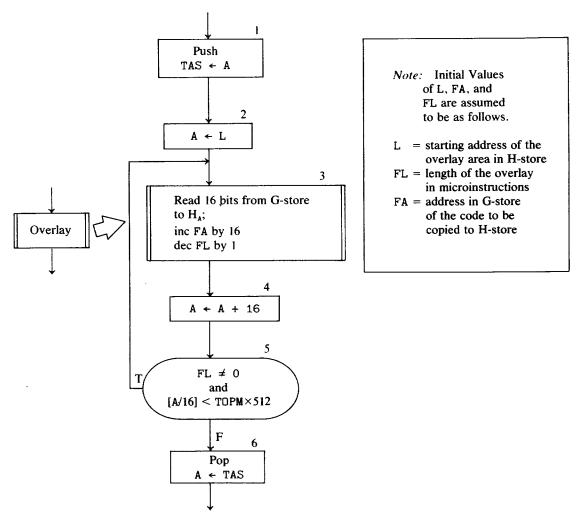

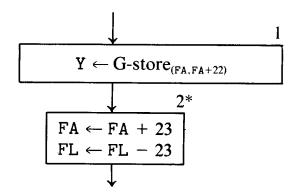

| 7.4    | Transfer of Microcode from G-Store to H-Store  | 161 |

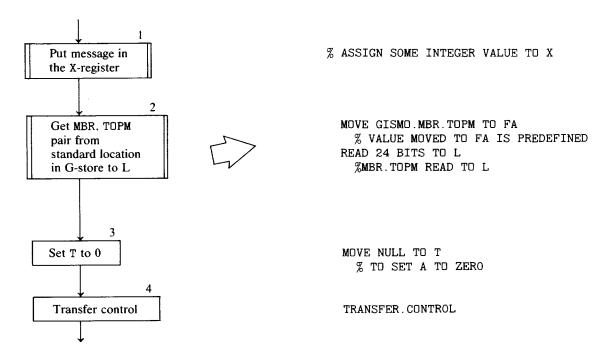

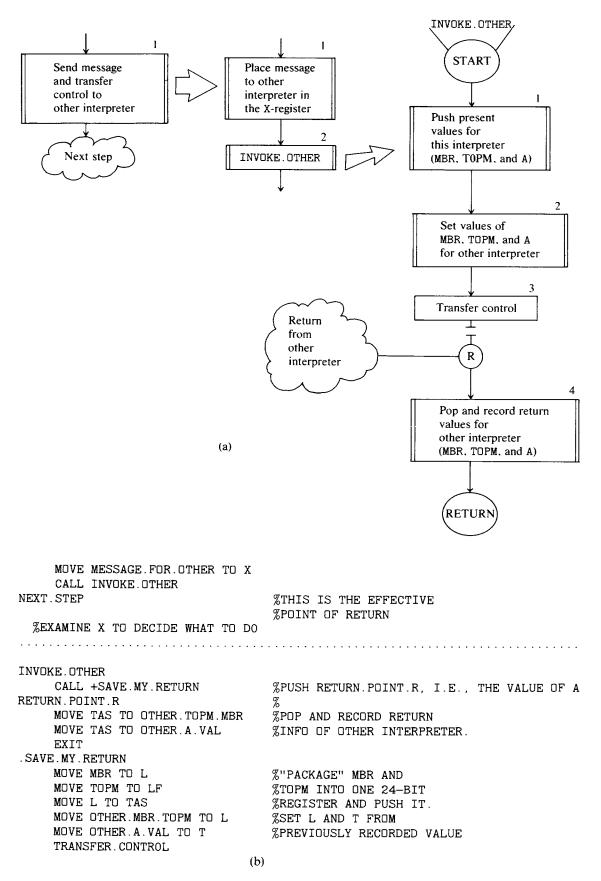

| 7.5    | Transferring Control to Another Interpreter    | 164 |

| 7.6    | Summary                                        | 168 |

|        |                                                | 180 |

| Appen  | lix A—Abridged MIL Reference Guide             | 170 |

|        | Directory                                      | 170 |

| 1      | Notation                                       | 172 |

| 2      | Executable MIL Statements                      | 173 |

| 3      | Nonexecutable MIL Statements                   | 205 |

| 4      | Special MIL Expressions                        | 210 |

| Appen  | dix B—Abridged Reference Guide to the B1726    | 212 |

| 1      | B1726 Register Summary                         | 212 |

| 2      | Testable Bits for IF Statements                | 217 |

| 3      | Microinstructions: Syntax and Semantics        | 219 |

| Appen  | dix C—A User's Guide to McMIL and SMACK        | 258 |

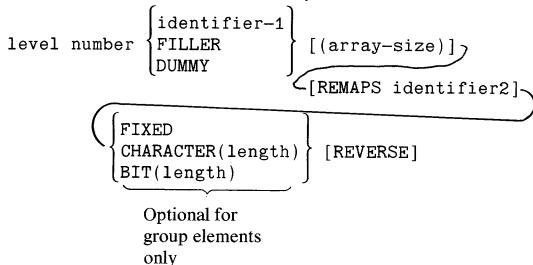

| 1      | McMIL Statement Syntax                         | 259 |

| 2      | McMIL Statements for the Operation             |     |

|        | of the SMACK Processor                         | 259 |

| 3      | McMIL Statements for Documentation             | 260 |

| 4      | McMIL Statements Used to Format the Listing    | 260 |

| 5      | McMIL Statements for Storage Allocation        |     |

|        | and Addressing                                 | 261 |

| 6      | McMIL Statements for Debugging                 | 262 |

| 7      | McMIL Statements for MCP Interface             | 263 |

| 8      | McMIL Statements for MCP Communication         | 264 |

| Conte | vii                               |     |

|-------|-----------------------------------|-----|

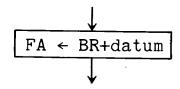

| Appen | dix D—Loader Primer               | 269 |

| 1     | The JCL Command Sequences         | 269 |

| 2     | Syntax of the Loader Card Deck    | 270 |

| 3     | Example                           | 274 |

| Appen | dix E—McMIL Listing               |     |

|       | for an Abridged SAMOS Interpreter | 275 |

| Appen | dix F—The SAMOS Computer          | 304 |

| 1     | The SAMOS Execution Cycle         | 306 |

| 2     | Instruction Repertoire            | 307 |

| 3     | Error Conditions                  | 307 |

| 4     | The SAMOS Loader                  | 307 |

| Index |                                   | 311 |

### **Preface**

The Burroughs B1700 family of computers exhibits a new style of architecture. These computers are known as interpretive definable-field machines. Their normal mode of execution is the interpretation of other computers, virtual or real. A system designed to interpret other computer systems should have a flexible storage-accessing mechanism so that bit strings of arbitrary length may be fetched and processed under control of the programmer. The definable-field feature of the B1700 family supports efficient interpretation of instructions and promotes effective use of storage. Overviews of these features were presented by W. T. Wilner in a series of papers in 1972 ["Design of the B1700", pp. 489–497, and "B1700 Memory Utilization", pp. 579–586, in AFIPS Conference Proceedings, Vol. 41, Part 1, and "Microprogramming Environment of the Burroughs B1700" in IEEE Computer Society COMPCON72, pp. 103–106.]

Innovative systems such as the B1700 and its successors are attractive laboratory facilities for education and research in computer science, especially for software engineering studies, including the design and evaluation of new or special-purpose computer and data-base systems, and for studies in software portability.

This book describes the architecture of the Burroughs B1700 family, with primary attention given to the B1726 computer system, its internal structure, and how it may be programmed for the emulation of other computer systems. The book may have only limited appeal to computersystem specialists who are looking for reasons to select one computer organization over another. We do not address the comparative strengths and weaknesses of the B1700. We do not address such interesting questions as why interpretation is important and when it is to be preferred over the more conventional compiler-based general-purpose systems popular today. We do not dwell on the history of interpretation nor on its potential for the future. (We only hint at the promise for multilevel interpreters.) Finally, we do not suggest other applications of the B1700 architecture, say for database computing. Rather, our objective is to help the person who is already motivated to learn the "insides" of the B1700 and who wants the knowhow to implement an interpreter at the microcode level.

The book grew out of a set of notes written for upper-level undergrad-

x Preface

uate computer-science students who have some prior knowledge of conventional computer-system organization and low-level language programming. Students at the University of Utah have used these notes in a software laboratory course in which the major objective is to produce a microcoded emulator for a fairly simple computer, e.g., a PDP-11. For more advanced students who expect to use the B1700 for research, the same notes have been useful for self-study as a supplement to or replacement for available reference manual literature.

The programming language introduced and used in this text, McMIL, is an enhanced version of MIL (Micro Instruction Language, an assembler for which is supplied by Burroughs). The McMIL superset of MIL contains statement types which can be used by the programmer to simplify the generation of MIL instruction sequences that correctly interface a MIL interpreter program with the system environment (e.g., for achieving interrupt handling, i/o management, file system services, and process switching).

The text consists of seven chapters and several appendices. The first three chapters focus on the architecture of the B1700 family as interpreting machines, on the internal structure of the B1700 processor, and on its (symbolic) micro-level machine language. The next three chapters show ways to write micro-level programs. A major case study vehicle that is used is a simulator for the hypothetical computer SAMOS outlined in Appendix F. It is in Chapters 4, 5, and 6 that the assembly language MIL and its McMIL enhancements are thoroughly illustrated. Methodologies of higher-level language programming including stepwise decomposition, clean structure, and good documentation are applied in translating from problem statements expressed in relatively abstract terms to concrete McMIL programs. Appendices A, B, and C are intended as reference manuals for MIL, for the actual computer system's register and instruction semantics, and for the McMIL extensions, respectively. (Appendix D provides additional reference materials used for setting up test runs of an interpreter, and Appendix E offers listings of the toy SAMOS interpreter and a sample test run. The toy interpreter may be used in a set of exercises as a study vehicle and point of departure for some interesting modifications and enhancements.) Chapter 7 examines the fine points in the control structure of the B1726 as a microprogram processor.

These seven chapters intentionally focus on the existing hardware of the B1700 family for use in design and implementation of interpreters and are to a great extent independent of the supporting software supplied by Burroughs. It is expected that another book would be useful for focusing on the structure and functions of the Burroughs software, Preface

including the operating system (MCP) and the critically important central module (known as GISMO) which serves as an i/o-device driver, process switcher, i/o buffer server, and interface with the MCP. Such a book would provide the reader with a serious look at the (system-controlled) environment which supports the execution of programs one has learned to write and test.

The authors acknowledge with deep appreciation the support of our colleagues, students, and secretarial friends at Utah who have helped us assemble this text. We are also most fortunate for the support received from the Burroughs Corporation. Many persons within Burroughs helped make the project at Utah and this book, one of the byproducts, a reality and, we hope, a success. We are grateful to all of these individuals. In particular, the project could not have become a reality without the help and confidence of R. R. Johnson, R. D. Merrell, and R. S. Barton, members of the Burroughs engineering organization who were early advocates of the B1700 as a system worthy of serious attention and use in computer-science and engineering studies. This book is published with the permission of the Burroughs Corporation.

E. I. Organick Salt Lake City, Utah

J. A. Hinds Goleta, California

# Chapter 1 Universal host computers

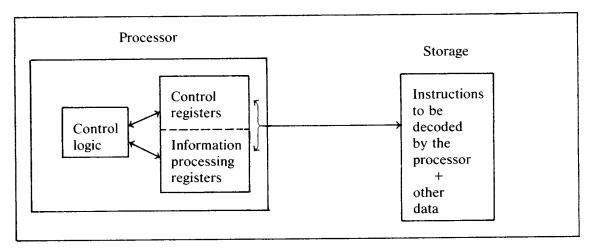

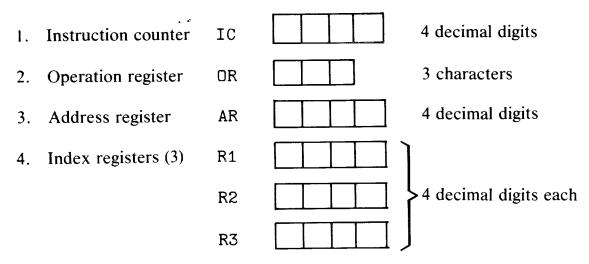

An important characteristic of conventional (von Neumann) computer systems is the *control mechanism*, or *processor*, which is designed to decode and execute a sequence of instructions fetched from storage (Figure 1.1). The processor generally has at least two groups of registers: one for control, and one for "processing information". The first set of registers is mainly used for controlling the sequence of instructions in the program and for decoding each instruction so that it can be properly executed. The second set of registers, nearly but not totally unrelated to the first set, is used in carrying out the execution of decoded instructions. Generally speaking, execution involves fetching (or storing) data from (or to) storage, or examination and manipulation of data fetched from storage or produced by the execution of preceding instructions.

The picture of the computing machine given in Figure 1.1 is clearly incomplete, since it lacks a connection to the storage in the outside world. The input/output (i/o) controls and devices provide channels for information to flow from or to the computing machine and the "outside" storage which may consist of various media (tapes, disks, displays, printed paper, etc.) For the present discussion we shall ignore i/o transfers to outside storage.

The tasks of actually decoding and executing each instruction of the computing machine are *primitive*. The programmer normally cannot influence the manner in which these tasks are carried out. In all early computers these primitives were achieved by hardware circuitry. In many recent computer designs they are implemented as sequences of microsteps or microprograms which are themselves interpreted by hardware circuitry. By one means or another these microprograms are often made inacessible to the programmer, so that interpretation of the instructions that a user programmer might compose remains primitive; i.e., he has no influence over the interpretation mechanism.

Although the programmer of a computer of this class may not vary the primitive behavior of such a computer, he may as an expedient compose a *simulator* (or *emulator*) program whose function is to interpret programs for other machines. The logic of the programmed interpreter is

Figure 1.1. A view of a typical computer architecture.

completely under the control of the user. Not only can he vary the steps of the decoding mechanism, but he also can select whatever execution logic he chooses.

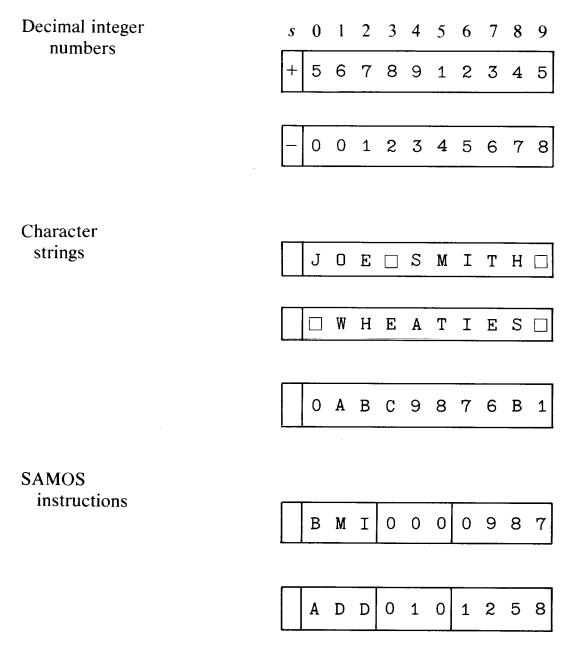

The user has a wide spectrum of redesign opportunities available. It may be that he wishes to simulate a machine that offers only a slightly different set of responses from that of the basic machine, e.g., augment its instruction set with a few more instructions, or alter the interpretation of the existing instructions. On the other end of the spectrum, he may have in mind the simulation of a machine having an entirely different set of instructions, with formats quite different from that of the "host" machine and having quite different semantics. For example, he may have in mind to emulate on a PDP-9 a PDP-15, a SAMOS machine,1 or a FORTRAN machine. The first one (PDP-15) is just an extension of the PDP-9 itself (i.e., has only a few new instructions.) The second (SAMOS), though quite different in its semantics (having decimal arithmetic rather than binary) is roughly similar in the syntax and semantic power of its instructions to that of the PDP-9. Thus the formats of both SAMOS and PDP-9 instructions are fixed in length and have a small number of fixed subfields, both use index registers, etc. On the other hand, the instructions of FORTRAN have variable formats, a variable number of subfields, and a much greater range of semantic complexity than those of the PDP-9.

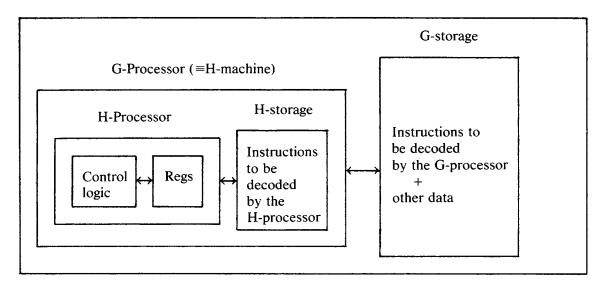

Figure 1.2 is a first view of a two-level host/guest system, consisting of a host, or H-machine, which functions as an interpreter of another computer system—G, for guest. Recursion in computer organization is

<sup>&</sup>lt;sup>1</sup> A hypothetical computer used for instructional purposes in certain introductory computer science courses. (See Appendix F.)

Figure 1.2. Structure of a two-level host/guest system.

clearly implied in this view.<sup>2</sup> Here we examine it from the inside out. The H or host processor consists of control logic and some storage (the registers). The H-machine consists of the H-processor and storage for its instructions (H-storage). But the H-machine in turn functions as a processor for another machine G, so the H-machine is in effect a G-processor. Adding "outside" storage for the H-machine forms a new machine (the G-machine). The outside storage for the G-machine is not actually shown in Figure 1.2, but its existence is implied (as was the outside storage for the machine depicted in Figure 1.1). In principle this recursion can be extended, since the G-machine might be designed to behave as a processor for some other machine G-G (guest of guest) and be coupled to storage containing programs for the G-G machine, etc.

There have always been practical trade-offs in building interpretive systems of this type. If the instruction set of the host machine and its registers is sufficiently different from that of its guest, the H-language subroutines which interpret G-language instructions may become long (and occupy a lot of H-machine storage). Also the time required to interpret a G-language instruction sequence on the H-machine may far exceed the time required to execute a "comparable" H-language instruction sequence executed on the same H-machine. Ratios of 10 to 100 for G-time/H-time are not uncommon. Even so, interpreters built to run on conventional computer systems are valued widely.

Since any machine may in principle be coded to behave as a host for any guest machine, it is also feasible that the same host may behave at

<sup>&</sup>lt;sup>2</sup> The concept that a processor may be viewed as having a recursive structure was first brought to the authors' attention by Robert S. Barton.

different times like the processor for any of a number of different guests. The backing store for an H-machine may contain interpreters for different guests. These interpreter programs may be swapped in and out of H-storage by some scheduling discipline, so that during discrete time slices the H-machine in fact acts like first one G-processor and then another. The duration of the time slices may be days, minutes, or seconds (or less), depending on the "swapping" technology that is used. Whatever the size of the time slice during which one of the interpreters is active, it should now be easy to accept the fact that any host may behave as a *universal* host, i.e., a host for a variety of guests.

Even so, few actual computer systems have been designed for applications in which they behave typically as hosts, much less as universal hosts for other machines. The B1700 class of computers, however, is one system which was indeed intended to behave mainly as a universal host. As we study it we shall hope to see in what ways its special features support such behavior.

The B1700 family of computer models, produced by the Burroughs Corporation, has been recently augmented with upgraded versions called B1800. In this book we will use the term "B1700" to refer to all members of this augmented class of computer systems except when we explicitly mention one member. For these systems the machine language of the host processor (H-language) is defined by the same base set of 16-bit microinstructions. Moreover, these systems have essentially the same internal logical structure, differing only in the mechanisms for accessing microinstructions. The B1700 has also been called an "interpretive definable field machine" because the programs and data executed by its interpreters are accessed from a storage that is viewed as an ordered set of *fields* (bit strings), each of *definable* length.

### 1.1 STRUCTURE OF STORAGE IN THE B1700 FAMILY OF COMPUTERS

To satisfy requirements of a universal host machine, the H-machine processor must have access to microprograms of many interpreters, one for each guest machine. One way to translate this requirement into an implementation is to imagine that the H-processor actually has access to several H-stores, each holding an interpreter for a different guest machine. Naturally, the processor must then be capable of switching from one H-store to another so that the system can multiprogram among several active interpreters. Storage technology and storage management techniques that have been developed over the past 15 years suggest several cost-effective ways by which such a system can be implemented.

Three related approaches have been taken in the B1700 family, one for each of three models within this family. These models are the B1710, B1720 and B1800.

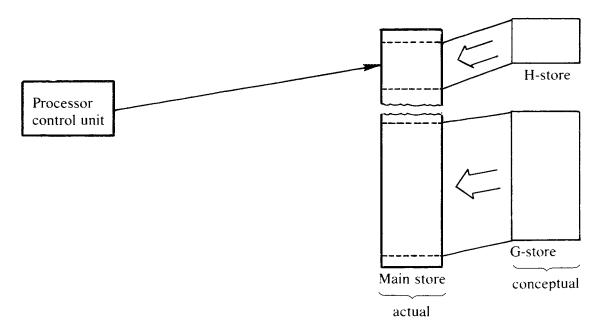

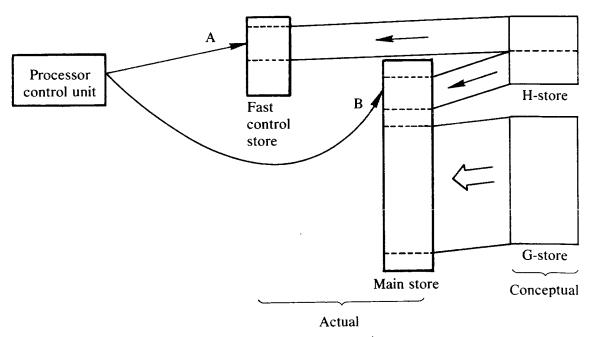

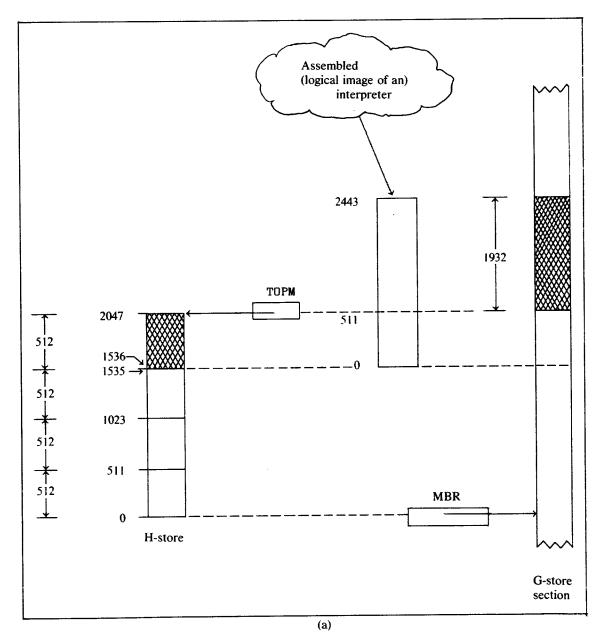

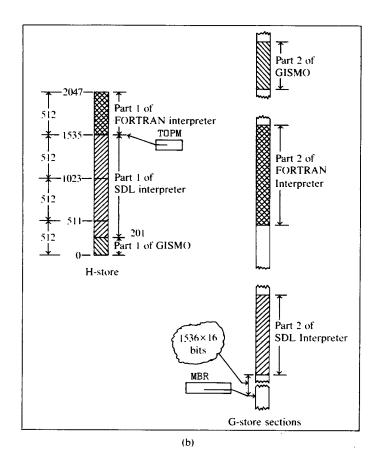

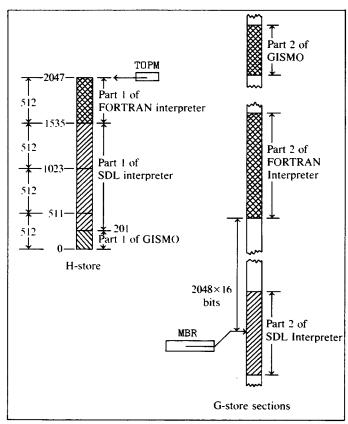

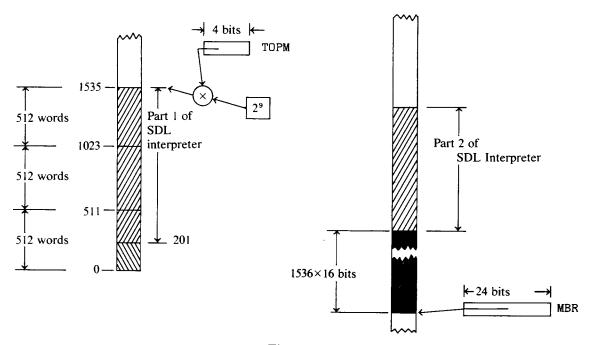

The first approach (simplest, least expensive in hardware and slowest) is found in the B1710 model. Here (Figure 1.3) main storage is allocated into separate sections, some representing H-store and some representing G-store. The section representing H-store holds the microprograms that comprise the interpreter for a G-machine. The figure shows only one G-store and one H-store section represented, but in principle and in practice the main store is large enough to hold several of each.

Each H-store holds the microprograms that constitute the interpreter for a G-machine. The B1700 processor can be initialized to begin fetching and executing microinstructions from any H-store section of main storage using a G-store section as its workspace. At any given moment the B1700 processor knows about (has access to) only one H-store and one G-store representation in main storage. Switching interpreters implies resetting registers of the B1700 processor so it has access to a different H-store/G-store pair.

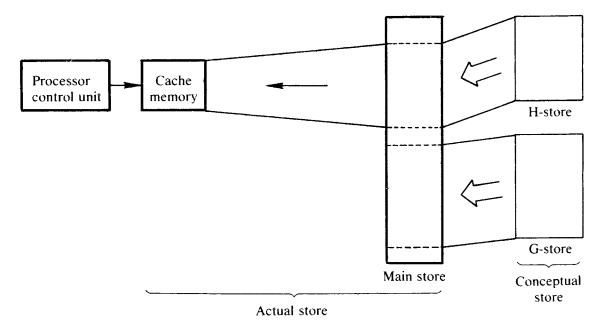

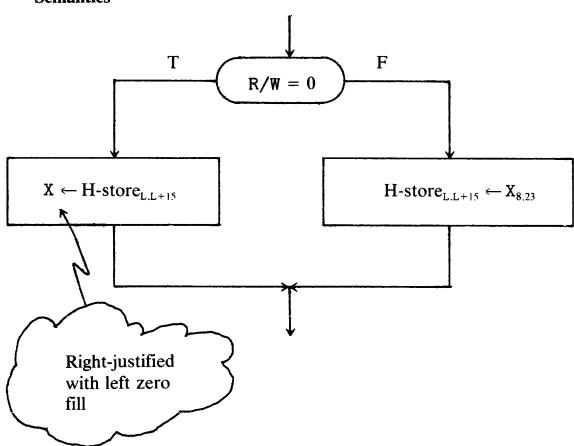

The B1800 model uses a similar principle for the representation of Hand G-stores in main storage, but is able to fetch microinstructions more rapidly through the use of a "cache memory" (Figure 1.4). The cache holds copies of blocks of microinstructions transferred from the main store as needed. The access to a microinstruction, when it is found in the cache (the usual case), is roughly an order of magnitude faster than the access to a microinstruction that must first be brought to the cache

Figure 1.3. B1710 Processor access to H-store code.

Figure 1.4. B1800 Processor access to H-store code.

from main store. The size of the cache is large enough to contain an entire interpreter, or at least that portion of it that is most frequently executed.

The B1720 model uses a less elegant but quite effective method for speeding up the fetching of microinstructions. A second storage unit, here called *fast control store*, is added to the system (Figure 1.5). This unit is large enough to hold the most frequently used portions of one or

Figure 1.5. B1720 Processor access to H-store code.

more interpreters, space permitting. H-store is represented in part in the fast control store and in part in main store, depending on the size of the available fast control store. Extra base registers are provided in the B1720 processor for use in determining the access path needed to fetch the next microinstruction, a path leading either to the fast control store (path A) or to the main store (path B). Other things being equal, the B1720 and the B1800 degrade gracefully to B1710-like performance as the size of fast control store or the size of the cache, respectively, is reduced to zero. Chapter 7 of this book deals with these details.

Other differences exist between the B1710, B1720 and B1800 models than those just mentioned, but they are unimportant for the purposes of this book. Nevertheless, to avoid fuzziness, we shall always be as specific as possible about which model we are discussing. Because the authors' experience at the University of Utah has been primarily with the B1720 model, in particular the variant known as the B1726, this book will describe the B1726; but in so doing it also describes the related models to a very large extent. When we have occasion to discuss one of the other models, we will be careful to identify it.

### 1.2 THE B1726 MODEL OF STORAGE

We can now gain additional initial perspective by focusing on how storage in the B1726 achieves the effect of a universal host machine. A typical mainstore, which Burroughs refers to as S-memory (S for string), normally has a size of at least 64K bytes (2<sup>19</sup> bits). The fast control store, which Burroughs refers to as M-memory (M for microinstruction) usually has a size in the range 4K to 8K bytes, enough to hold at least 2048 H-language, 16-bit microinstructions.

Let us first assume that the B1726 is busy executing programs for only one G-machine. [Later we will consider the more general case of two or more different G-machines as simultaneous guests on the host B1726.] And further, let us assume that the one G-machine interpreter needed consists of about 4096 microinstructions, or twice that of the available H-store. Then we expect that at some point in time the main-store S-memory will hold half of the G-machine interpreter. If there are more G-machine language programs active (i.e., being executed in multiprogram-ming mode), then storage will be needed for procedures of each program and for the data sets of each program. [If two or more programs shared certain procedures, duplicate copies of those (reentrant) procedures will not be needed. So the remainder of S-memory will be occupied by various procedures and data structures of the active programs of the guest machine.]

Any time the host machine needs to execute a microinstruction from H-store that is not in the M-memory, one of three approaches can be taken:

- 1. A block of microinstructions, including the ones currently needed, can be swapped in from S-memory, replacing a selected block of microcode now present.

- 2. So long as the microcode has the attributes of a pure procedure (read only), a simple overlaying strategy will also work, making swapping unnecessary. This also assumes that a backup copy of the entire interpreter is kept in S-memory.

- 3. Since the B1726 processor is so designed that individual microinstructions can also be fetched into the instruction register directly from S-memory (not just directly from M-memory), only the frequently needed microinstructions need be fetched from M-memory.

When blocks of microinstructions are needed in control store, approach 2 is used. (Approach 1 is never needed or used, since microcode is treated as pure procedure.) The B1726 executive system known as "MCP" (Master Control Program) also uses approach 3, since H-store microinstructions may be fetched directly from either M-memory or from S-memory.

To summarize, our conceptual G-store maps onto the physical storage called S-memory, and our conceptual H-store maps, to a first approximation, onto the physical storage called M-memory; but in actuality, since M-memory is a relatively scarce resource, H-store maps onto S-memory as well. It will be convenient and simpler to adopt the more ideal view, that of a one-to-one correspondence, which is H-store onto M-memory and G-store onto S-memory. We will take this simpler view in the next five chapters without loss of rigor. In the last chapter (Chapter 7), however, we will need to examine the details of the actual mapping between conceptual and actual host stores in the B1726 system.

To appreciate the motivation for the "two-level control store" of the B1726, it is important to observe the following.

1. Because the M-memory is regarded as a relatively scarce resource, the different interpreters being multiprogrammed can if necessary reside on and be executed entirely from S-memory. The operating system has responsibility for keeping track of which physical storage resources currently hold the interpreters, and is able to redistribute all or part of each interpreter among the two levels of storage as deemed appropriate.

2. If the operating system allocates the most frequently used portions of one or more interpreters to M-memory, there need be little need for frequent reallocation. This is because in general much more is known about the control structure and frequency of use of an interpreter and its parts than is known about the higher-level language programs that will be interpreted; hence it is possible to dedicate a portion of the M-memory resource to particular interpreters for relatively long periods of time with better effect than would be possible in a conventional system whose fastest storage is used for currently executing user or system code that is derived from compilers.

# Chapter 2 The B1700 as an interpreting machine

The computer known as the B1700, or more precisely (in our laboratory) the B1726, is a system designed to make easy and as efficient as possible the interpreting of a wide variety of instruction sets. The machine language of the B1700 host is very low-level, resembling the microcode of other systems whose programmable machine language is at a higher level. A very low-level machine language is advantageous for programs that interpret instructions which are at the semantic level of conventional machine language or even higher-level languages. Although we shall refer to the machine language of the B1700 as microcode, we should take care to avoid the heretofore common connotation of microcode as something fixed (e.g., read only) and inaccessible to the computer user. In our case "microcode" is merely the manufacturer's name for the machine language of the B1700.

The B1726 is a general-purpose computer. Like all such machines it may be programmed (in this case in microcode) to interpret another machine. There is, however, one major practical difference. Most general-purpose computers have instruction sets designed to go with a storage organization that is word- or byte-oriented. Bit strings fetched from storage are always taken in fixed chunks (words or bytes) aligned on chunk boundaries. Moreover, the length of the machine's instruction is always made strictly compatible with the chunk sizes fetched from storage. Usually the length of an instruction is one chunk or a multiple thereof. We take it for granted, for example, that for the 18-bit wordorganized storage of the PDP-9 there is a companion instruction set, every member of which is an 18-bit chunk. Instructions of the PDP-9 are fetched or stored in units of 18 bits on aligned 18-bit boundaries (i.e.,  $\equiv 0$ modulo 18.) Now the PDP-9 may not be a perfect computer, but without knowing more about its internal organization, we may assume that what it does best is done on chunks of 18 bits. Thus, if we were to use the PDP-9 to interpret instructions for a 17, 19, or 20 bit computer, we would expect to see a waste of storage as well as a distinct loss of efficiency in both the decoding and execution functions of the interpreter. What we have just said about the PDP-9 applies equally well to all such conventional word- or byte-organized systems.

Is the B1726 any different in this respect? Very definitely, yes, but the difference is somewhat subtle. On the one hand, its own machine language involves a set of microinstructions of fixed length (16 bits). However, within this repertoire are instructions which control the width and position of bit-string fetches (and stores) between storage and the processor. Thus, to fetch a string of 17 bits from bit addresses 19367 through 19383 takes no more and no fewer B1726 machine instructions than, say, fetching a string of 21 bits from bit addresses 8001 through 8021.

These controls for fetches and stores actually only regulate the flow of bit strings of from 1 to 24 bits in length. For transmission of chunks greater than 24 bits, the B1726 provides simple but powerful iteration controls in its machine-language repertoire. So although it takes more instructions (and more time) to fetch a 25-bit chunk than a 24-bit chunk, all chunks in the range 25 through 48 are in the same get/put class (instructions and time for a fetch or store), as are chunks in the range 49 through 72, 73 through 96, etc.

Apart from the crucial capability for defining fields of bits (chunks) and transmitting them from or to storage, the B1726 organization resembles in essence the familiar von Neumann architecture of a modern (e.g., 4th generation) sequential stored program digital computer. Because of its special orientation (and objective) as an interpreting machine, however, the structure of the processor, at first glance, appears to be more complicated than a conventional processor. Even so, it is easy to gain a simplifying view of this structure if one realizes that the processor performs only four types of activities; one can gain an integrated understanding by studying these activities one by one. There are interconnecting data and control paths between the registers used to implement each activity so a complete understanding of the processor can come only after all these interconnections and interrelationships are recognized. The four activities are

- 1. Data fetch and addressing

- 2. Data examination and manipulation

- 3. Decoding of higher-level language instructions

- 4. Control

We will look briefly at each of these.

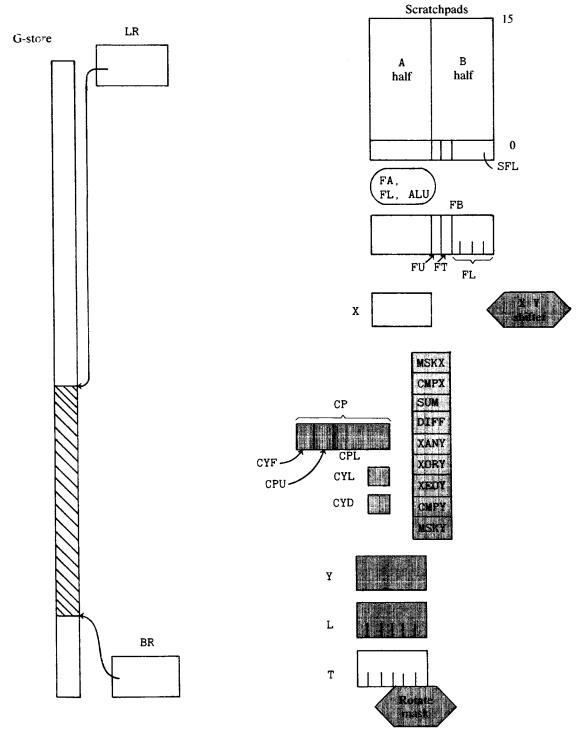

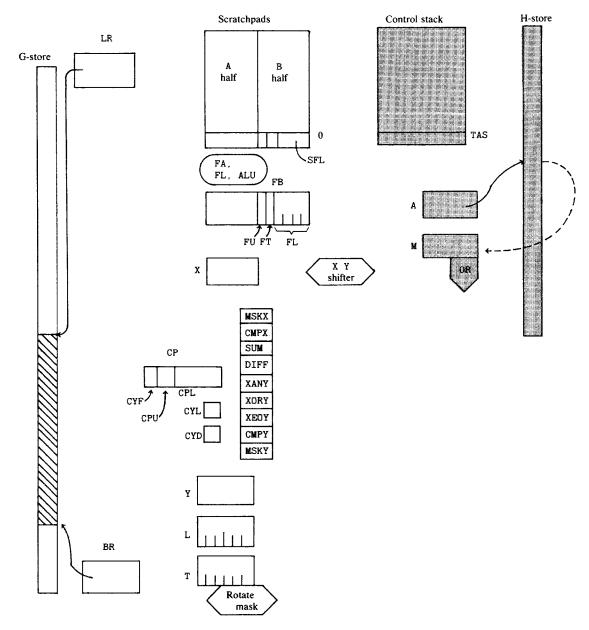

1. There is a group of registers associated with the control and transmission of chunks to and from data storage. These include, for example, registers to hold the starting address of a bit field in storage, field length, etc., as well as registers to serve as receivers (from storage) or sources (to storage). Other registers, in a block

- known as the *scratchpad*, are useful for holding bit addresses and lengths for frequently referenced fields in storage.

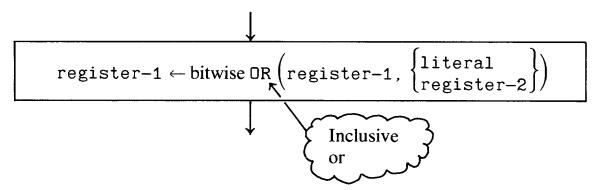

- 2. There is a group of registers associated with the arithmetic and logical functions of the computer, so that the B1726 can be microcoded to perform the conventional types of arithmetic and logic needed in everyday (simpler) computer and systems applications.

- 3. A few registers are available for use as *local storage*. Some of these are endowed with special properties, very useful in the decoding phase of the interpreting process (e.g. shift and rotate, and in addition, extraction and testing of subfields).

- 4. The machine has what amounts to an instruction or program line counter and an instruction register for controlling the sequence of microinstructions and for holding the microinstruction that is being decoded and executed by the *hardware*. In addition, there is a small stack whose main use is for holding return addresses for microprocedure calls (a control stack.) Address modification and other dynamic altering of B1726 microinstructions is made easy by utilizing a feature that ORs the operand of the preceding instruction with the next instruction. In many conventional machines this feature is achieved using index or base registers.

There are a number of explicit and implicit "connections" between the registers involved in the four classes of functions of the processor. Learning all these connections will take some time; the best way is by first studying some examples (case studies) of short microcode sequences. By tracing these one can incrementally accumulate an understanding of the whole process and be able to start writing B1700 microcode and/or "critiquing" microcode written by someone else.

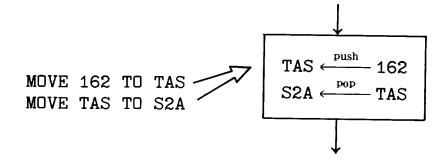

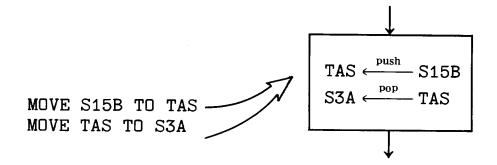

The explicit connections referred to in the preceding paragraph are those spelled out in each microinstruction. For example, each MOVE microinstruction explicitly names the *source* and *sink* registers involved in the move operation. In essence, it is possible to move bit strings from any register to any other register. Of course, there are certain exceptions—for example, the microinstruction that causes a fetch from storage names the sink register explicitly, but does not name the registers holding the bit address or length of the source field in storage. These registers are always implied, as is (for example) the accumulator in the conventional SUB instruction of SAMOS.

### 2.1 INSTRUCTION DECODING

In the introduction we hinted that the B1726 instruction set and machine organization were designed especially to facilitate interpreting

of guest-language instructions. That's a broad statement. There are potentially an infinite number of guest languages with an infinite variety of instruction formats. It is surely not the case that the B1726 decodes with equal facility the instructions of every possible guest or G-machine. First note, however, that for most actual machines (potential G-machines) the instructions formats are regular. That is, they have such characteristics as fixed length and fixed fields, or a very small number of lengths and a small number of different fields and field lengths, according to the subclass within the repertoire. Based on this set of characteristics, SAMOS, for example, has a regular instruction format. So does the PDP-9 or even the IBM System 370. Regularity is popular in actual machines for minimizing the complexity of the interpreting hardware and/or micrologic so as to gain maximum speed or economy.

But it is certainly possible to imagine other G-machine languages where the instruction formats are, may, or should be highly irregular or *exotic*. If the G-machine has a phrase-structured language such as ALGOL (or any of the so-called higher-level languages), chances are the instruction format will be regarded as exotic in comparison with those of most everyday conventional computers.

In a well-designed interpreting machine the work of decoding should be roughly proportional to the complexity of the instruction format—and this appears to be true for the B1726 design. Whether regular or exotic, decoding is easiest on the B1726 if the operation code field is at or near the left end of the instruction. But fortunately, this is the case in nearly every machine design we have seen. Why is this so? Well, op-code fields are typically positioned at the left end of an instruction, with operand fields following, to conform with the customary functional notation of mathematics, e.g., f(a,b) for a two-operand operator f. To fetch and decode such an instruction, two steps are necessary.

- 1. First we position the storage pointer to the storage address of the first bit in the instruction, and then read into a B1726 register as many bits as are needed to examine the entire op-code field. For a G-machine with 256 or fewer distinct binary op-codes (that covers most G-languages), the op-code field might then be no more than 8 bits in length.<sup>1</sup>

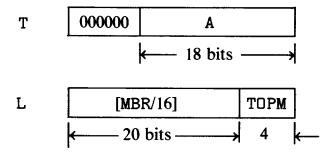

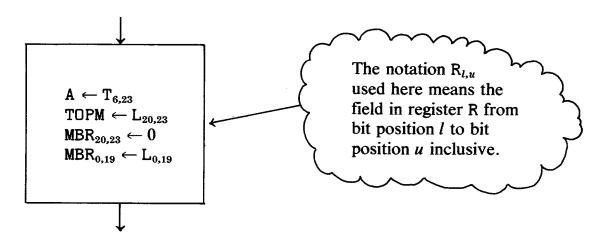

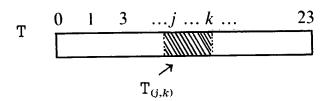

- 2. In the B1726 there is a 24-bit special decoding register, known as the transform register T, which has been endowed with special logic. In

<sup>&</sup>lt;sup>1</sup> Of course there are various ways of designing operation codes, which for the sake of efficiency, might lead to op-codes of various lengths, some less than 8 bits and some more, in this case. [But, for pure binary computers it is certainly unlikely that an op-code field greater than 24 bits would ever be required.]

particular, there are B1726 machine-language instructions which test bits of T and bit subfields of T, extract them, and move them to other registers. The B1726 possesses other features which enable a rapid jump (much like a FORTRAN computed G0 T0) to the appropriate subroutine, where further analysis of the instruction or its execution can commence. For such jumps, the op-code extracted from the special decoding register T serves as index value for the jump (i.e., jump to here plus index.)

If the G-language is regular, and if the instructions are 24 bits or less in length, then the entire instruction can be analyzed directly from one loading of the T-register described above. If they are of regular format, but greater than 24 bits, then two or more successive loadings of T from storage may be required. After each loading of T, subfields can be extracted from T, analyzed, and held as necessary in other B1726 registers that serve as local or temporary storage.

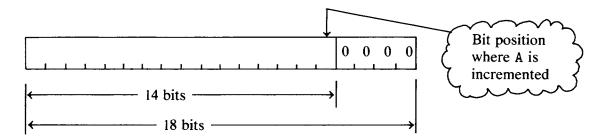

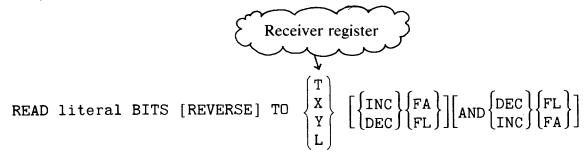

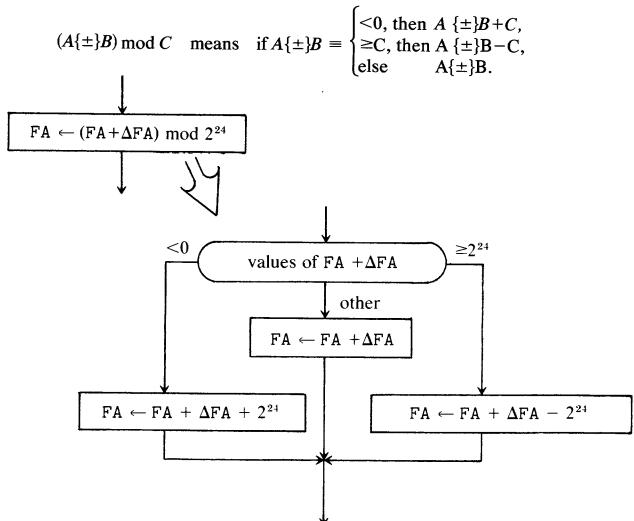

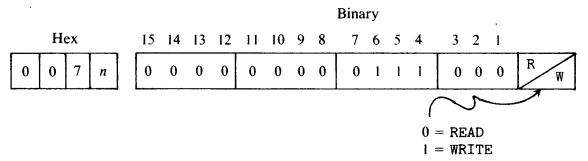

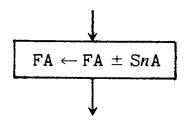

For each new loading of T the storage pointer must be reset to the bit address of the next field in storage. There is a special *field address* register in the B1726 called FA which is used for the purpose of holding the storage address of the next 24-bit (or smaller) chunk. To go with the FA-register, there is an adder dedicated for the purpose of incrementing or decrementing FA. One can specify activation of this adder, for adding or subtracting a small constant (0 through 24), as part of the microinstruction that uses FA. For example,

### READ 8 BITS TO T INC FA

specifies that T is to be loaded with an 8-bit field from G-store beginning at the address given by FA. Following the fetch from G-store, FA is to be incremented by 8. (The incrementation of FA overlaps the fetch of the next micro instruction from H-store.)

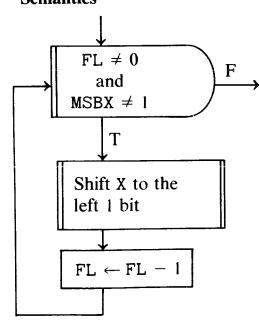

Another register called the *field length* register, FL, is provided in the B1726, and is also outfitted with a dedicated adder. The content of the FL-register is often used as an iteration counter for loop control during the transfer of long fields (>24 bits) to or from storage. If an instruction subfield is of variable length, the value in the FL-register can be preset to the (current) field length and then decremented and tested (against zero).

The specification for activating the FL's adder, like that for the FA's, is made part of the transfer microinstruction (READ or WRITE), e.g.,

WRITE 12 BITS TO T INC FA AND DEC FL, so there is no extra cost in B1726 machine time to carry out the address and counter arithmetic during each transit of the transfer loop. In this way, a series of variable-size subfields can be read from G-storage, the size being dependent on the analysis of preceding fields within the same G-language instruction.

# Chapter 3 Organization of the B1726 microprocessor

In the preceding section we identified four kinds of activities performed by the B1726 microprocessor. We now look at these one by one in more detail.

### 3.1 DATA FETCH AND ADDRESSING

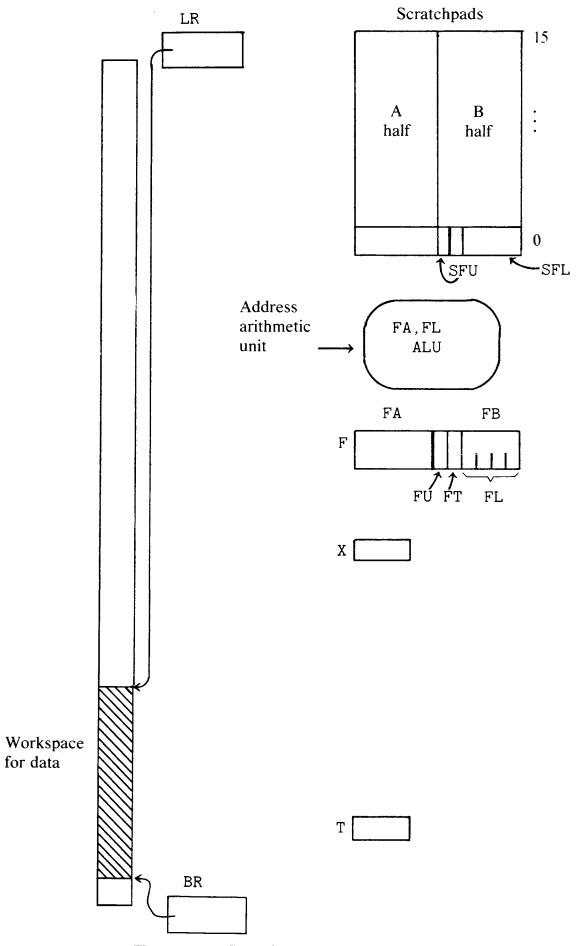

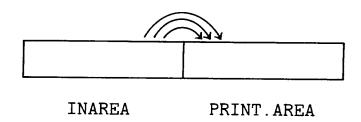

Before an interpreter can decode a higher-level instruction, it must be fetched from the store that holds it. We have called that store the guest store, or G-store (although the Burroughs literature calls it "S-memory"). We assume that before interpretation begins, the G-language program has been loaded into one portion of G-store and a workspace has been allocated for data storage for the same program.

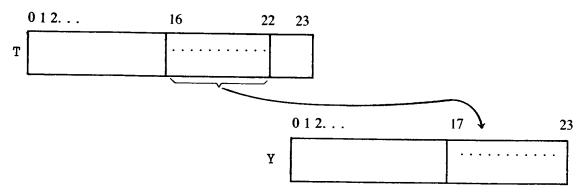

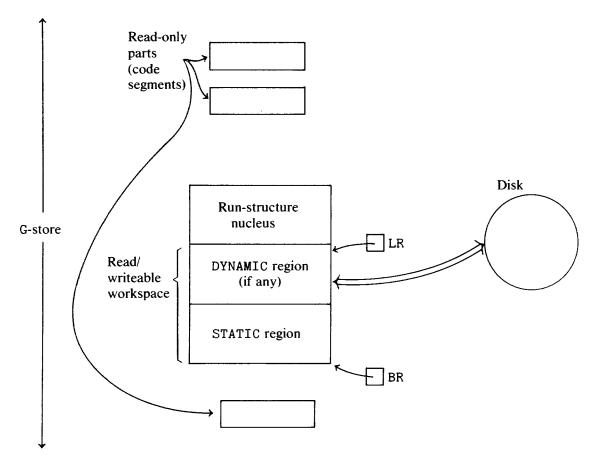

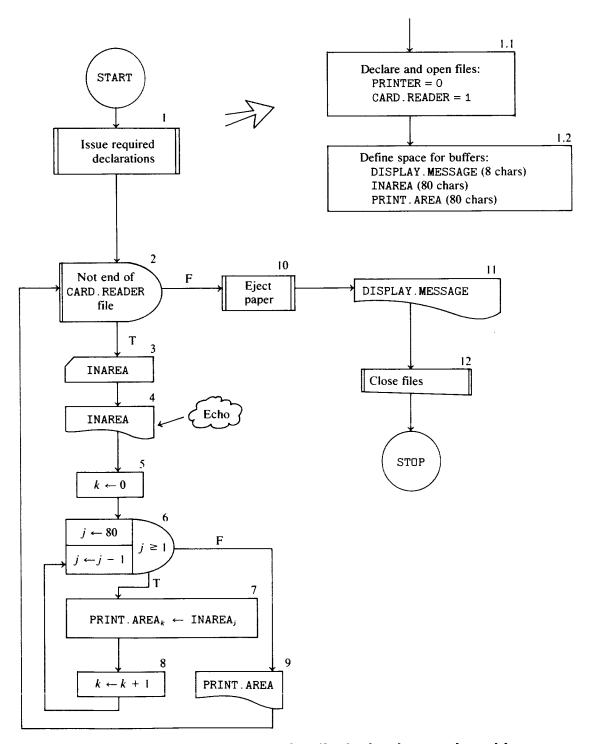

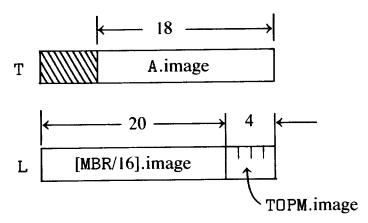

The left side of Figure 3.1 shows the G-store on a long "stick" to represent a bit string. A subfield to be used as the workspace is marked off by values in a pair of bounds registers called BR (base register) and LR (limit register). (The workspace is used for variables, constants, temporary storage, saved copies of registers during temporary interruption of the interpretation process, etc.). The bounds registers are used mainly to protect against accidentally writing into sections of G-store lying outside the workspace. The sections outside the workspace normally hold G-language instructions, i.e., code, system-manipulated input/output buffers, and workspaces for other computations that are being multiprogrammed with this one. We assume that the interpreter is provided with the size and location of the workspace and that the base and limit registers are set prior to interpreting the first G-language instruction.

The hardware logic of the microprocessor checks each G-store data

<sup>&</sup>lt;sup>1</sup> We use the term microprocessor to mean a processor of microinstructions (i.e., as a shorthand for microinstruction processor. We do not intend to imply that the B1726 computer system is a tiny computer consisting of a few large-scale integrated (LSI) chips. A principal reference describing the processor is: Burroughs, "B1700 Systems Reference Manual", Burroughs Corporation, Detroit, 1972, Form 1057165.

Figure 3.1. Data fetch and addressing.

address before using it against values of the LR and BR register. If the LR and BR registers are preset properly, and if they are not improperly reset during execution of the G-language program, the programmer can be assured that the process of interpretation will not damage system tables. But caution must be exercised, since there are no constraints in the machine language against assigning values to LR and BR. Having said all this about the protection role of LR and BR, we will for the most part now ignore these two registers, taking for granted that the microcoder who develops an interpreter will use these key registers properly.

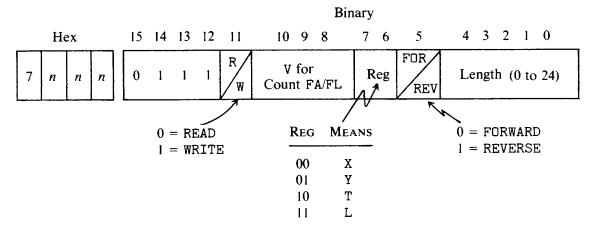

We are now ready to see how inputs from G-store (reads) and outputs to G-store (writes) are executed. The read (or write) action is a hardware procedure that has three parameters.

Bit address of the field in G-store

Length of that field

Register in the microprocessor that is to serve as *sink* (for a read) or *source* (for a write)

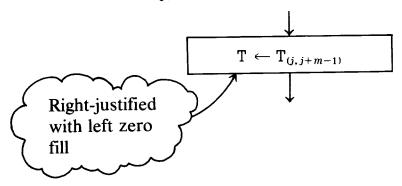

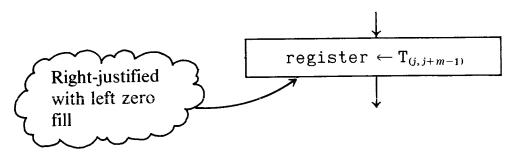

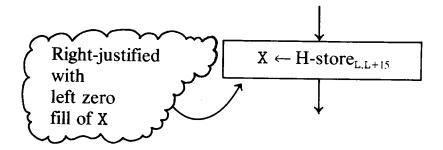

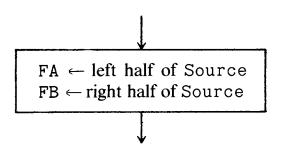

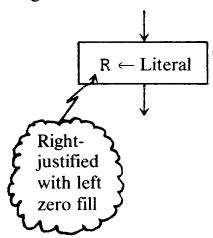

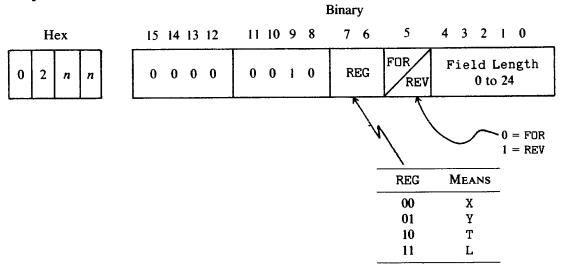

An argument value for the first parameter is (must be) always provided by presetting the FA register with the bit address of the beginning of the G-store field. [In Figure 3.1 we see that the F-register is a double-length register, the left half being the 24-bit FA register. G-stores of up to 2<sup>24</sup> bits are possible in the B1726, so an absolute address is 24 bits long.] The second argument may be specified explicitly in the read (write) microinstruction, or by a default rule. The third argument is always specified explicitly. The registers X and T shown in Figure 3.1 are two of four registers that can be named as the sink (source) registers in a read (write) microinstruction.

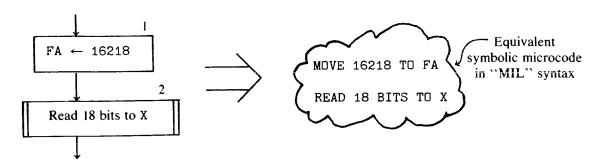

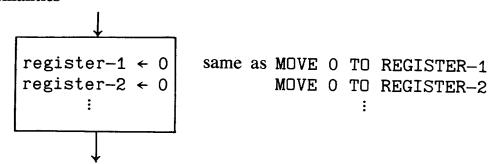

Example Suppose we are trying to read an 18-bit field located at bit address 16218 into the X-register of the microprocessor. The steps we want to execute are

What could be simpler? This sequence would cause the transfer of 18 bits at address FA to register X. The X-register is one of four 24-bit

registers (others are Y, T, and L) which may serve as a sink (or source) for reads (or writes) from (or to) G-store.

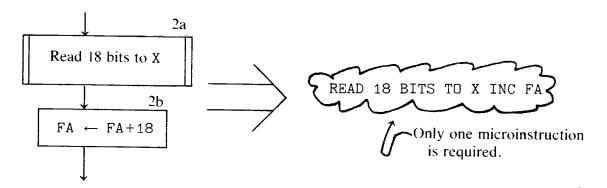

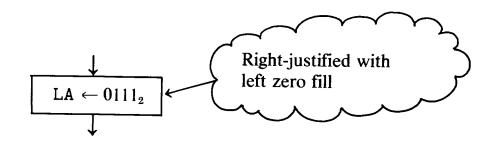

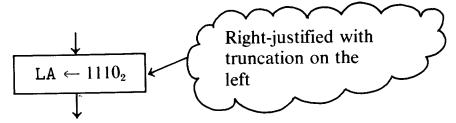

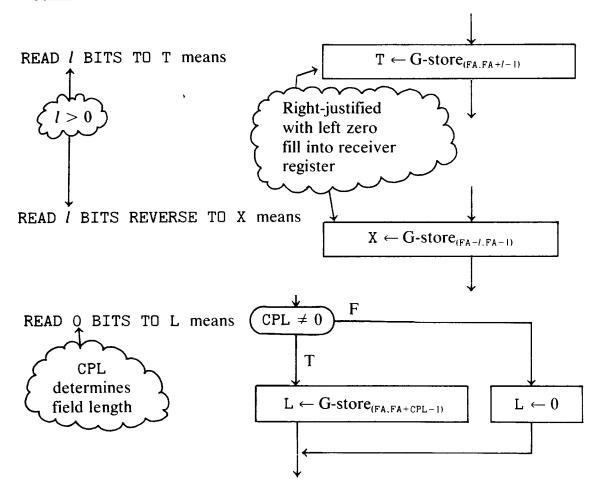

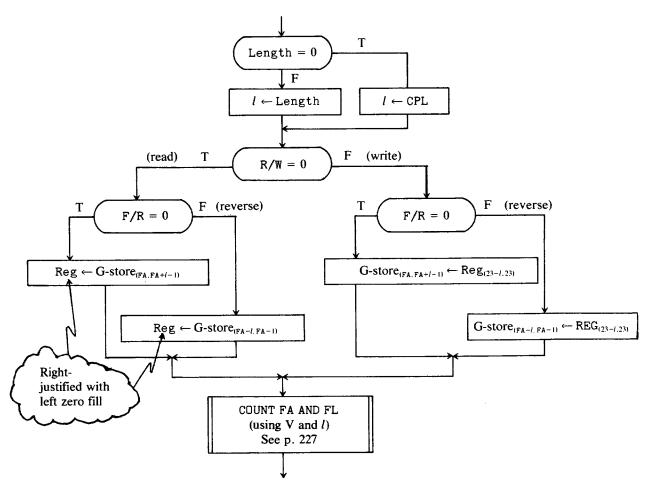

One READ (or WRITE) instruction is sufficient to transfer from 1 to 24 bits. [Fields of fewer than 24 bits are regarded as right-justified in the sink (or source). Zeros pad the left end of the sink register when the input field is less than 24 bits long.] How are fields of length greater than 24 bits to be transferred? Clearly, a microinstruction loop is needed such that upon each transit of the loop, up to 24 bits are shipped. Of course, FA must be properly incremented for use in succeeding reads or writes. A special arithmetic unit is provided in the B1726, shown in Figure 3.1. Using this facility we can make the READ (or WRITE) instructions specify incrementation (or, if we like, decrementation) of FA immediately following the transfer of bits from/to G-store. In particular,

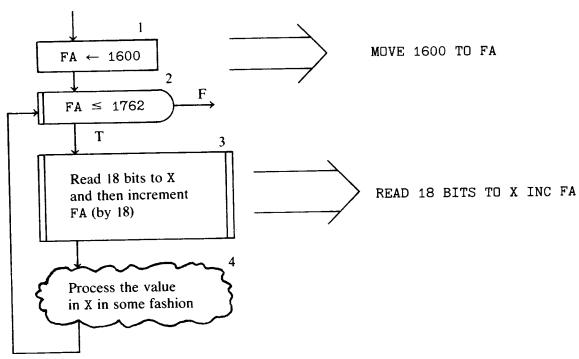

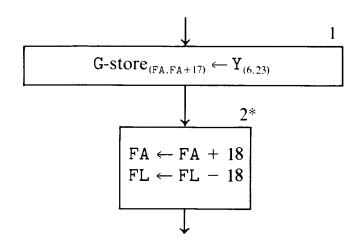

Combining the incrementing of FA with the READ (or WRITE) in this way will cut down the number of instructions needed for loops involving repeated transfers. For example, the loop in Figure 3.2 shows how one might control the transfer of a sequence of ten 18-bit fields (or one 180-bit field taken as ten 18-bit chunks) into the microprocessor, where the starting address in G-store is 1600.

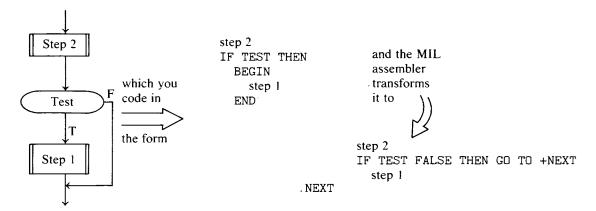

We already know how easy it is to map boxes 1 and 3 into B1726 symbolic microcode (or MIL,² for micro implementation language). It is not however, straightforward to map box 2 above into microcode, simply because on the B1726 there is no circuitry to perform a logical comparison on the value in FA. As mentioned at the end of Chapter 2, the B1726 designers have solved this problem in another, relatively convenient, way. They provided another register, FL, in the lower 16 bits of the right half of F to serve several purposes, including that of a loop counter. The address arithmetic unit will increment (or decrement) FL as well as FA, if such action is specified in a READ or WRITE microinstruction. Moreover, contents of FL can be compared with zero. A skip or GO TO based on this comparison can then be taken based on

<sup>&</sup>lt;sup>2</sup> Appendix A of this book is an abridged reference manual for the MIL language.

Figure 3.2. Controlling a loop for reading a sequence of ten 18-bit fields.

Figure 3.3. Input loop and equivalent MIL code.

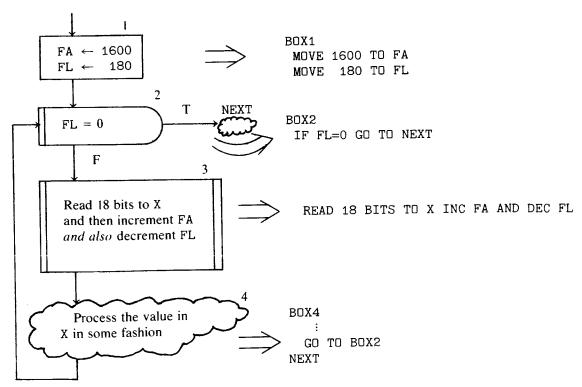

this test. Figure 3.3 shows a modified flowchart for the above input loop showing the use of the FL register as a loop control counter, counting by 18.

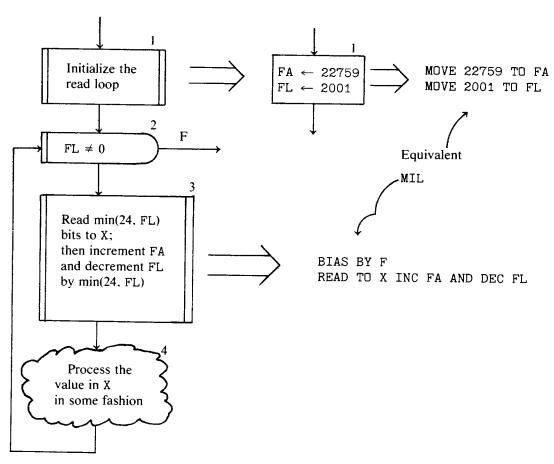

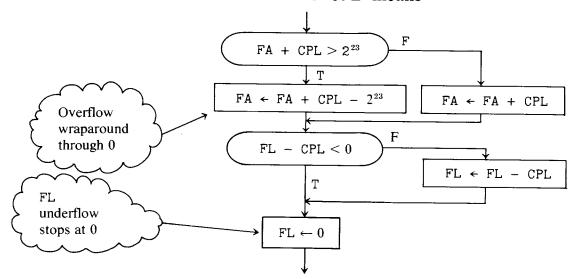

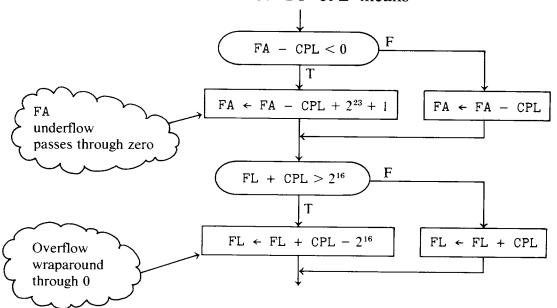

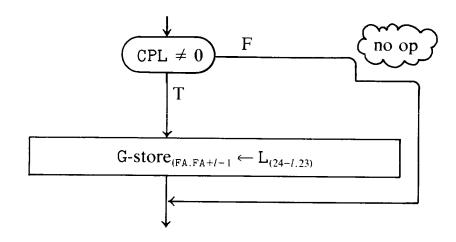

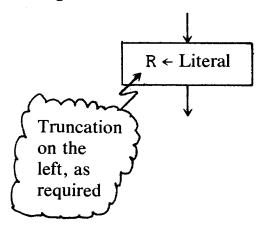

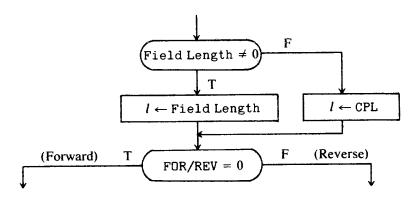

The approach taken in Figure 3.3 is all well and good when the width of the field moved from (or to) G-store is a multiple of the chunk size transferred during one READ or WRITE. What about other cases? For example, suppose we wish to transfer a field of 2001 bits, up to 24 bits at a time—i.e., as a sequence of 83 chunks of 24 bits, followed by one 9-bit chunk—starting at bit address 22759. It will be most convenient if all READs can be performed by one instruction which is part of the loop, including the one that transfers the residue of 9 bits. Figure 3.4 shows a flowchart representation of this type of read loop. Here again the FL register serves as a loop-control counter, but it also has one other important role.

These two illustrations (Figures 3.3 and 3.4) show how the FL register gets its name, i.e., the field-length register. This register may be initially assigned the actual length of the long G-store field to be transferred.

Figure 3.4. Read loop to transfer a field of length  ${\rm FL}$ ,  ${\rm CPL}$  bits at a time, into the X-register.

Fields up to 2<sup>16</sup> bits long may be accommodated in the B1726. [That's why FL is 16 bits wide.] We want to set the size of the chunk transferred by the READ instruction to the minimum of 24 and the current value of FL, which is to be decremented by 24 following each READ. When there is a residue chunk of 1 to 23 bits remaining to be transferred, it will be transferred on the last transit to the loop, the size of the residue being min(24,FL).

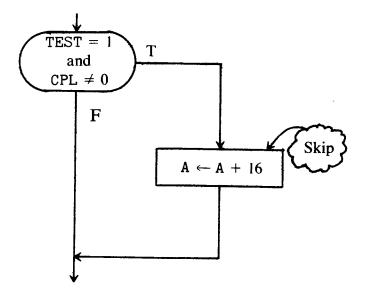

To see how this *residue control* is achieved in the equivalent B1726 operations, we must note two more facts about the semantics of the B1726 READ (and WRITE) microinstructions.

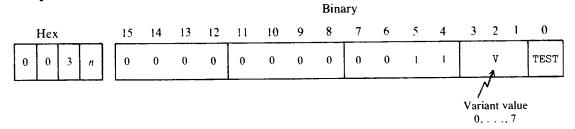

- 1. If the chunk size is not explicitly specified in the READ (or WRITE) instruction (or if it is explicitly specified as zero), a default value is chosen as the current value in the special length control or CPL register (not shown in Figure 3.1 but shown in Fig. 3.8 below).

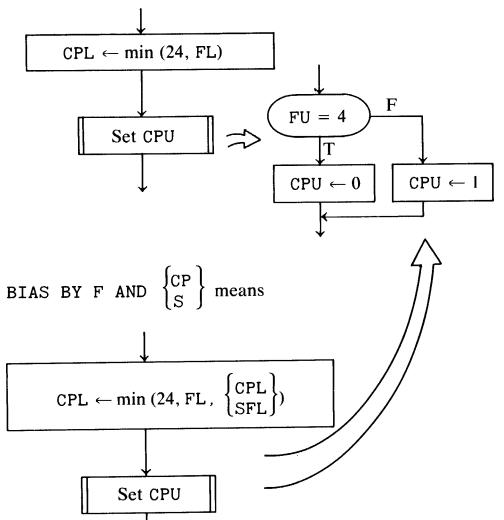

- 2. The READ (or WRITE) instruction may be preconditioned by execution of a so-called BIAS instruction, which sets the default chunk size by assigning to CPL the minimum of 24 and the value specified in that BIAS instruction. For example, executing the microinstruction

### BIAS BY F

prior to executing a READ with an unspecified chunk size amounts to

$$CPL \leftarrow min(24,FL)$$

,

which is precisely what is wanted for handling the residue in our field-transfer algorithm of Figure 3.4. In that instance FL had the value 9 and CPL the value 24 when the BIAS instruction was about to be executed for the last time. Executing the BIAS instruction at that point gives CPL the new value 9, so the chunk size used in the succeeding READ is 9.

Here are two final notes regarding field transfers:

1. In the example of Figure 3.4 we imagined that we wanted to minimize the number of READs by transferring 24-bit subfields (the largest chunk that can be transferred at one time). We are, of course, free to specify chunks of less than 24 bits. For example, had we chosen to transfer subfields of 7 bits each, only two coding

changes are required. In box 1, we need to insert the instruction

In addition, the BIAS instruction of box 3 must be written as

The semantics of this variant of the BIAS instruction is

$$CPL \leftarrow min(24, FL, CP)$$

Executing this instruction before each READ (or WRITE) guarantees that CPL will be set to the minimum of 7 (the value first assigned to CPL) and any lower value that may be eventually assigned to FL. Each READ will now transfer a chunk of 7 bits, except possibly the last transfer, which may be less than 7 bits. Incrementing of FA and decrementing of FL will now be done by 7 instead of 24.

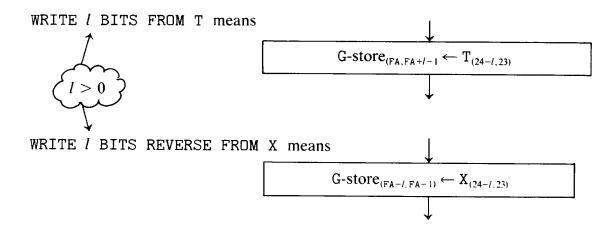

2. READ and WRITE microinstructions may proceed not only forward, (i.e., from low to high G-store bit addresses, which is the usual way) but also in reverse (i.e., from high to low G-store bit addresses). The READ REVERSE or WRITE REVERSE option is provided by the B1726 designers so the programmer can gain increased efficiency in certain types of transfer operations. For example, with FA set at a bit address as shown below,

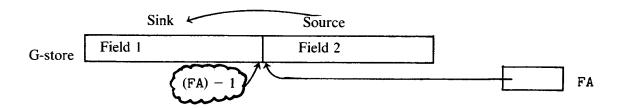

one can READ TO X (forward) from field 2 of G-store, and later WRITE REVERSE FROM X into field 1 without having to use a different value of FA. Suppose, for example, that fields 1 and 2 are each 16 bits long, with the address of the leftmost bit of field 2 currently in FA. If field 2 contains the character string "BC", then upon executing the sequence

READ 16 BITS TO X

WRITE 16 BITS REVERSE FROM X

the value stored in field 1 is also "BC". A REVERSE transfer does

not reverse the order of the information in the transferred copy. It only changes the significance of FA from the field beginning at address FA to the field ending at FA -1.

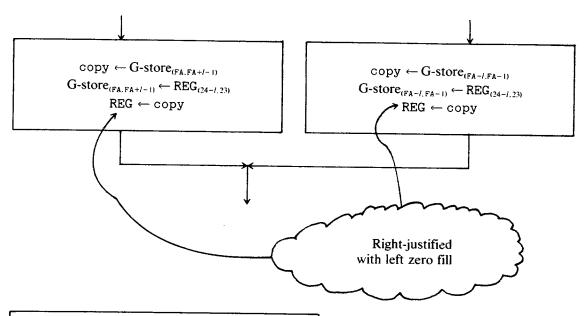

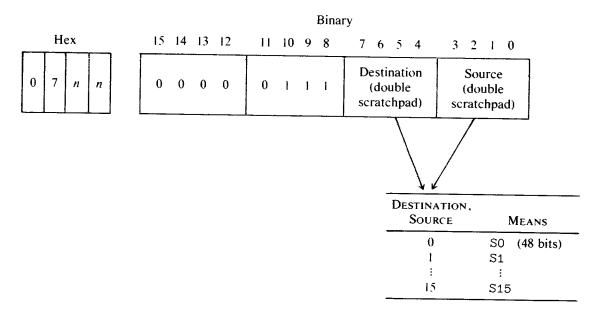

We have now explained the functions of most of the registers shown in Figure 3.1 except the "scratchpads". These are a set of 16 double-length registers which may be used as local storage for any purpose, but are especially convenient for the temporary storage of G-storage field descriptors, i.e. (address, length) pairs.

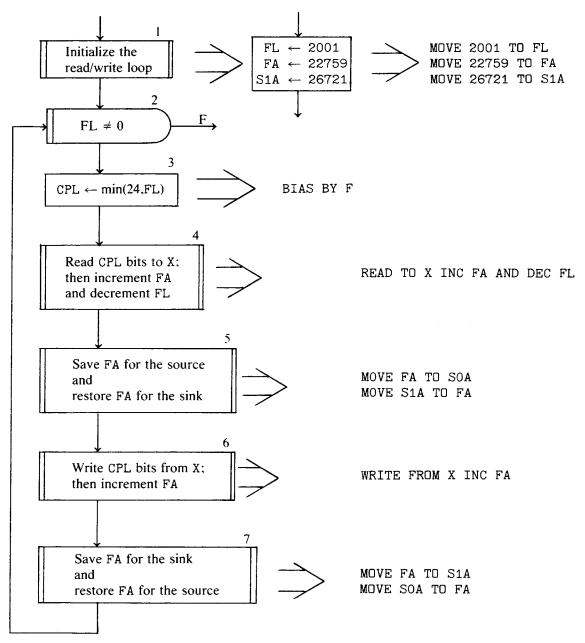

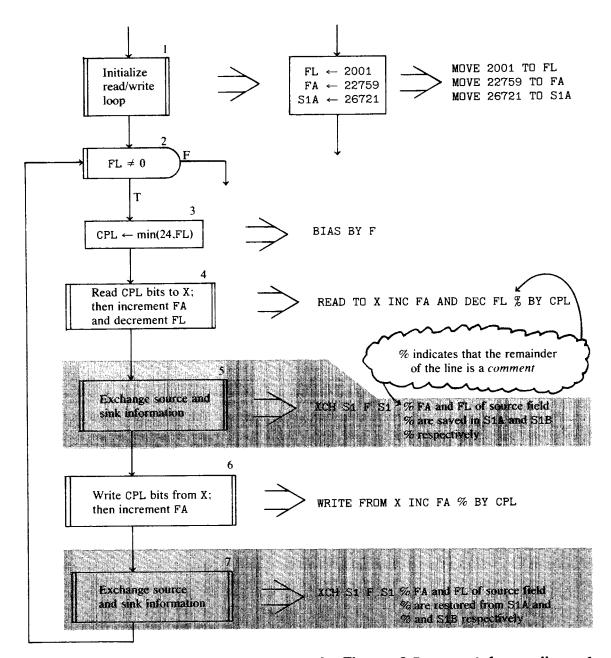

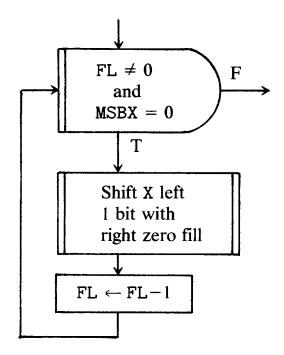

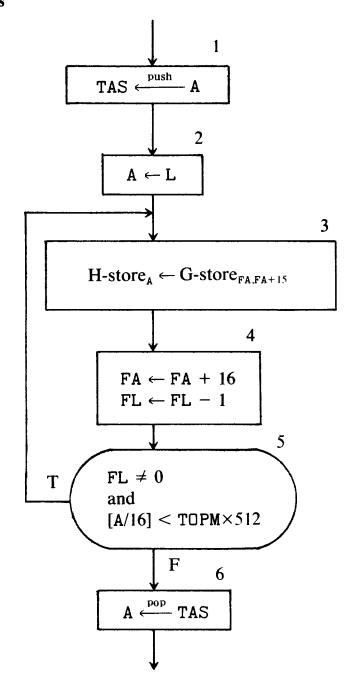

One obvious use of the scratchpads occurs to us if we consider the simple problem of copying a bit string from one part of G-store to another. For example, we shall consider the problem of copying a field of 2001 bits from a starting address of 22759 to a new field, starting at (say) 26721.

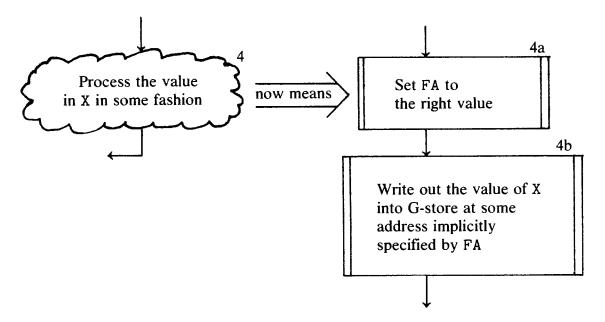

We saw in Figure 3.4 how to flowchart the task of moving this bit string from G-store into the microprocessor via register X. Now we want to take the chunks originally brought into X one by one, and write them out to G-store. Thus

But to achieve this objective, we need temporary storage to save and restore alternately the current values of FA for the source and sink fields on each transit of the loop. We can use scratchpad registers for this purpose, as suggested in Figure 3.5. S1A is used for temporary storage of the sink address, and S0A as temporary storage for the source address. The FL register is used as a loop control counter.

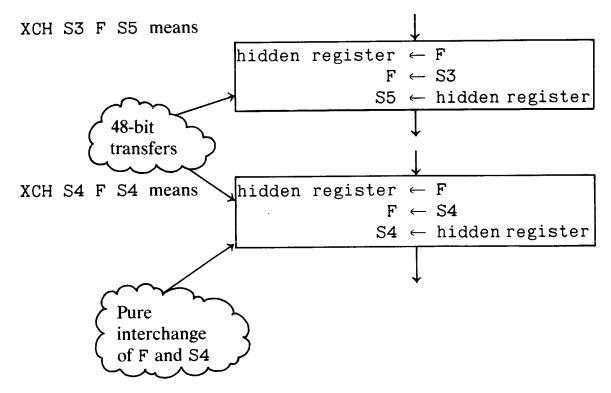

Another way to achieve the alternation of source and sink addresses, which saves two MIL instructions, takes advantage of the XCH microin-

Figure 3.5. G-store-to-G-store copy loop for a 2001-bit field, using separate scratchpad registers for saving source and sink addresses.

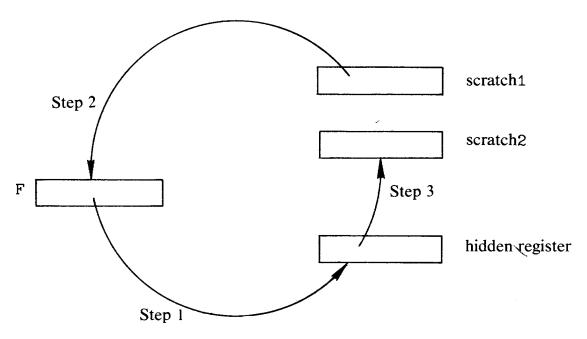

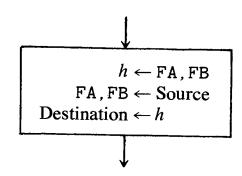

struction to interchange the contents of any scratchpad register (all 48 bits) with F. [The general form of the XCH is

which "simultaneously" moves a copy of F into scratch2 and a copy of scratch1 into F. In our special use of XCH in Figure 3.6, scratch1 and scratch2 are the same registers. We assume that the XCH operation uses

Figure 3.6. Same copy program as in Figure 3.5 except for coding of boxes 5 and 7, which uses the  $\rm XCH$  instruction and scratchpads  $\rm S1A$  and  $\rm S1B$ . (This program uses  $\rm S1B$  but not  $\rm S0A$ .)

a hidden register to simulate the simultaneity inherent in the exchange

where step 1 must precede steps 2 and 3.]

As the operations on the data flowing from G-store and back again become more elaborate, it will be increasingly convenient to hold at one time a variety of descriptors in the scratchpad registers. That is why 16 double registers hardly seems too many. [There are, however, some good arguments for not making the scratchpad too big. We shall discuss this issue in connection with the job of saving and restoring the state of a computation following an interrupt.]

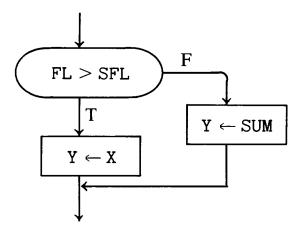

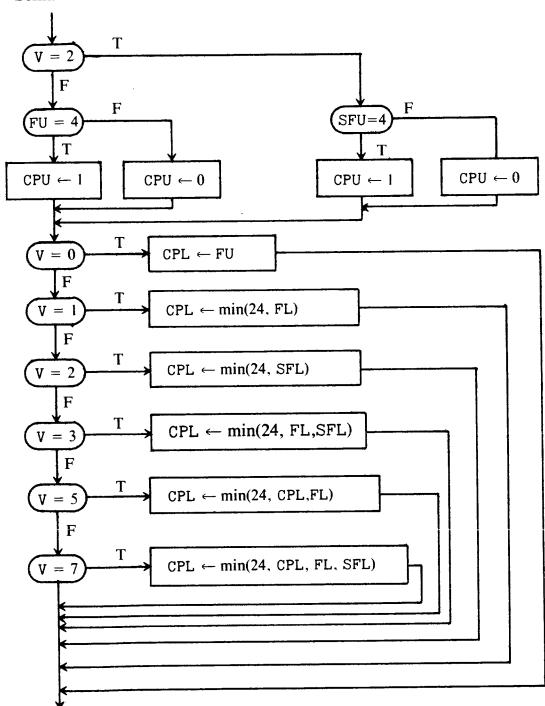

At this point we have discussed all the registers shown in Figure 3.1 except the 16-bit register SFL (in the lower-order portion of S0B, the right half of S0) and several 4-bit registers, namely FU, FT, and SFU. The SFL register may be used as a limit value against which FL may be compared. That is, the hardware senses the relative magnitudes of FL and SFL (<,=,>) and sets a bit in one of several control registers to be discussed later. Testing that bit can be used as a basis for branching, i.e., skipping the next microinstruction.

The SFL field may also be hardware-sensed in a variant of the BIAS instruction. For example, BIAS BY F AND S means CPL  $\leftarrow$  min(24,FL,SFL). It might be used, for instance, when S0 and F contain descriptors for two fields and the size of the next read or write chunk is to be based on the smaller of the length fields FL and SFL of the respective descriptors, thus avoiding destruction of G-store information when the source field is longer than the destination field.

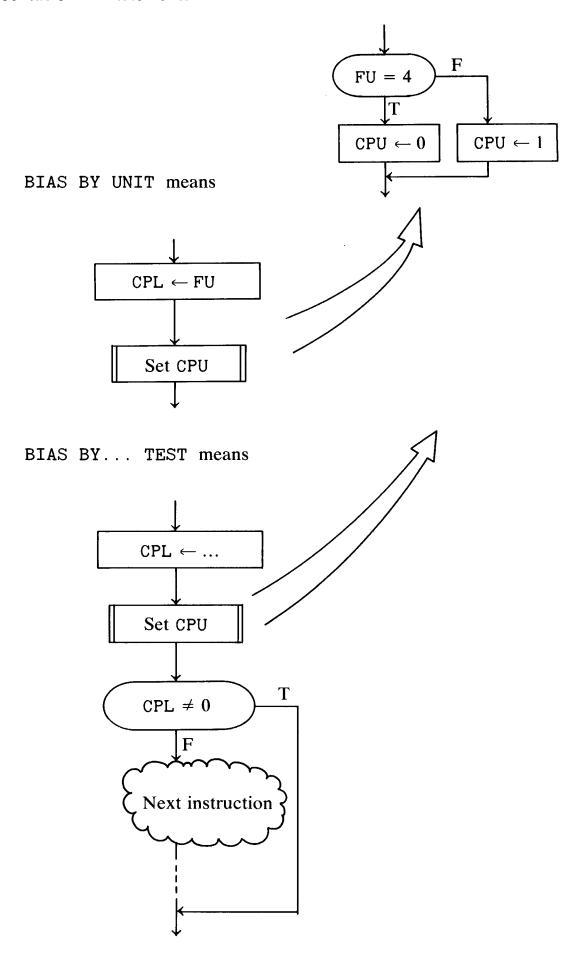

The four-bit registers FU, FT, and SFU have no important hardware function for data transmission to and from G-store. [Actually, the

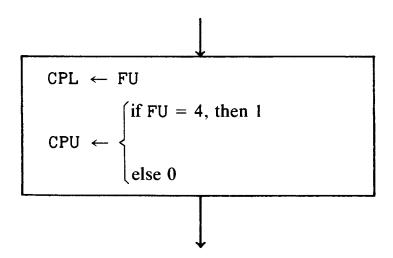

contents of FU may be sensed in a rarely used variant of the BIAS instruction, BIAS BY UNIT, in which UNIT is the key word that refers to FU. The contents of FU characterize the type of data (i.e., bit string, 4-bit decimal). The meaning of BIAS BY UNIT is

This has the effect of setting the chunk size to that of FU. The significance of the CPU and the value assigned to it is secondary. We will discuss the significance of the special CPU register later when we discuss the so-called "24-bit function box".] Data stored in FU and FT may be regarded as "addenda" to the address and length of a descriptor. In particular, when it is necessary to carry a type description for a field, such information may be held in FU and/or FT.

#### 3.2 DATA EXAMINATION AND MANIPULATION

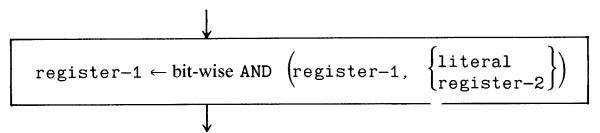

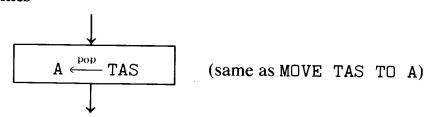

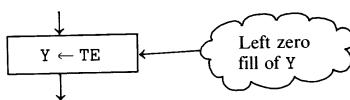

Once data have arrived from G-store into the H-processor, there are a wide variety of facilities for examining and processing them. As mentioned earlier, there are actually four registers, X, Y, L, and T, that may serve as receivers. Each is 24 bits long, and each has a set of distinct functional properties such that, depending on what one wants to do with the data arriving from G-store, one particular receiver register (X, Y, L, or T) may be more suitable than another. Of course, data can be moved (copied) from the receiver register to another one using the MOVE microinstruction. For example, if data has been read to T, it can then be moved (copied) to X:

READ 15 BITS TO T MOVE T TO X

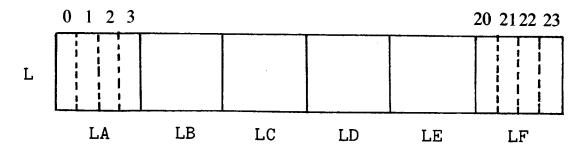

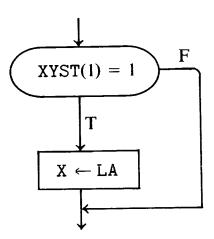

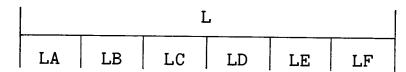

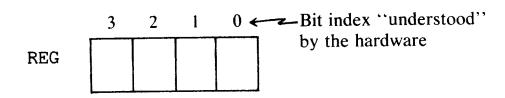

The L and T registers are further subdivided into individually address-

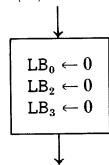

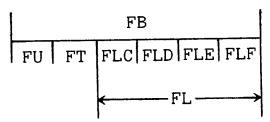

able 4-bit subregisters, known as LA, LB, LC, LD, LE, and LF:

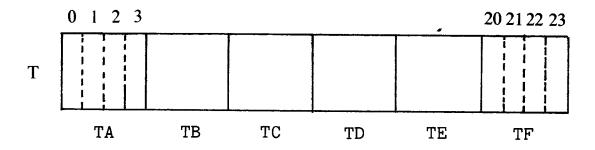

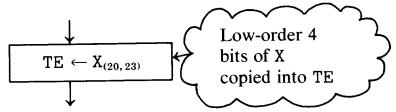

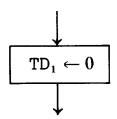

and TA, TB, TC, TD, TE, and TF:

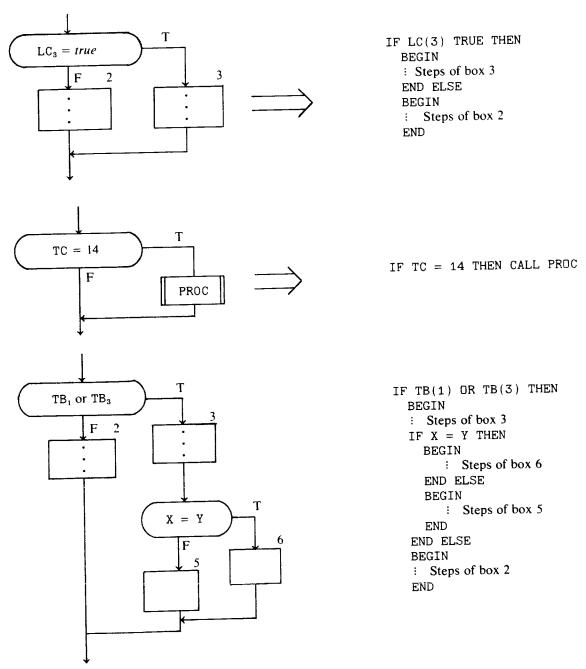

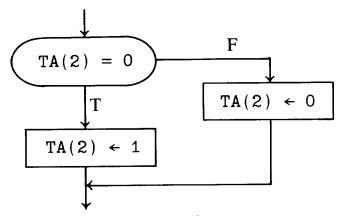

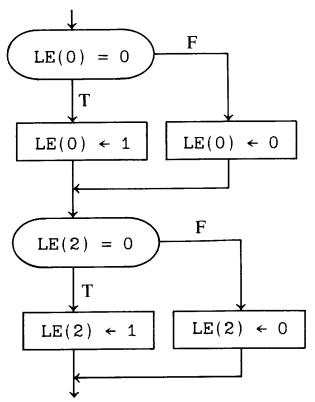

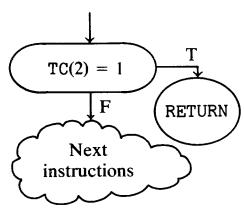

That is, each of these subregisters may be mentioned by name in a microinstruction. For example, MOVE LC TO TD would cause the four bits in LC to be copied to the TD field of T. The individual bits of a four-bit register are addressable from left to right with subscripts 0, 1, 2, or 3 respectively. Thus LC(3) is the same as L(11).

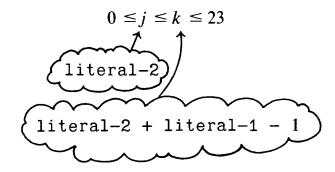

The T-register has rather special (and powerful) transformational properties. Its contents may also be tested as a basis for conditional branching. Perhaps even more interesting is the fact that *any* subfield of T may be copied and moved to any receiver register (X, Y, L, or T), using the so-called EXTRACT microinstruction. For example, a copy of the seven-bit field in positions  $T_{16}$  through  $T_{22}$  can be assigned to the lower-order seven bits of Y (and Y padded with leading zeros), e.g.,

The (MIL) microinstruction to achieve this type of copy is EXTRACT 7 BITS FROM T(16) TO Y.

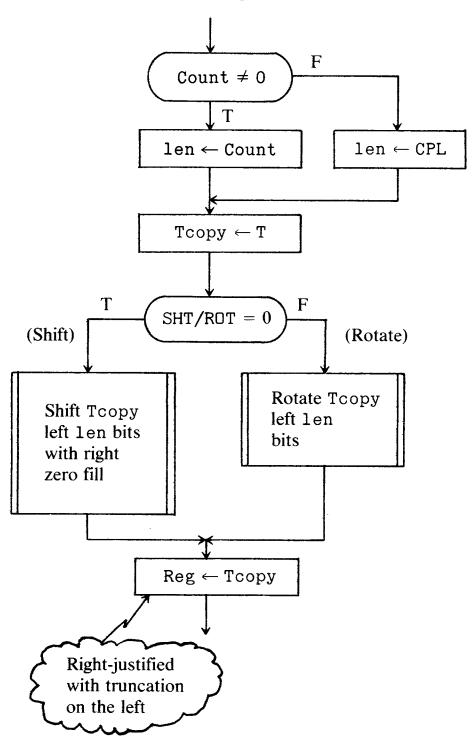

Extraction in the direct sense just described cannot be performed on the other receiver registers. However, two of the registers, X and Y, may be shifted or rotated left or right to isolate a desired subfield.

Any bit within L or T, or pair of bits that are within any one four-bit subregister of L or T, may be tested (compared for equality against particular values) for use in selection steps. Some example selection steps, mapped into MIL code, are given in Figure 3.7. The illustrations

Figure 3.7. Examples of selection steps based on contents of bits or pairs of bits within a subregister of L or T, or based on a comparison of X and Y.

given in this figure are intended only to provide an idea how easy it is to express tests based on the contents of the receiver registers or on one or two bits within one subregister. The syntax of the MIL IF statement is detailed in Appendix A.

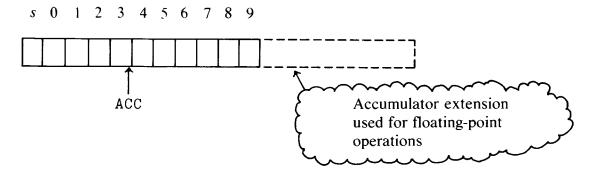

# 3.2.1 The arithmetic capability or "function box"

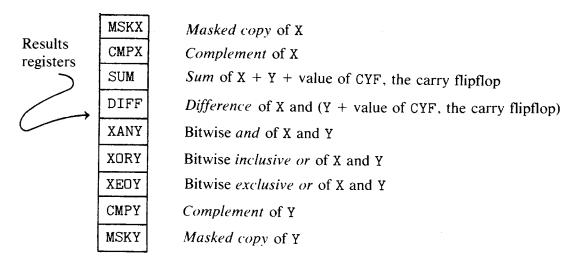

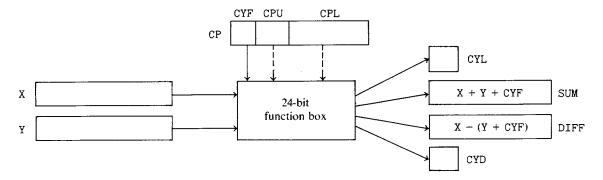

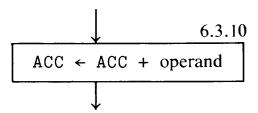

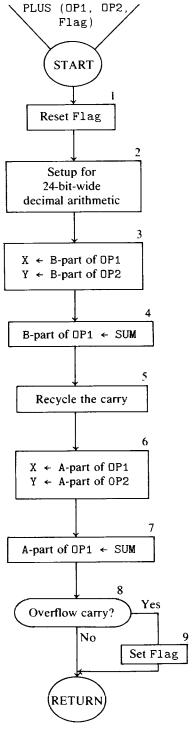

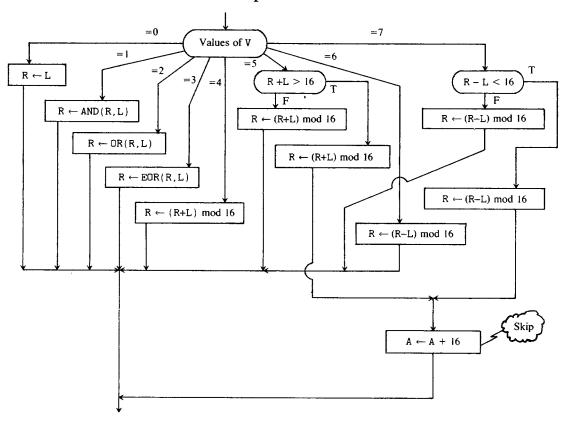

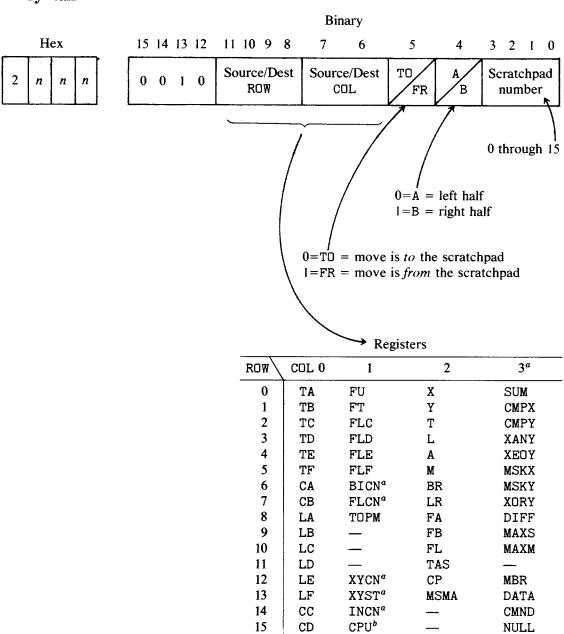

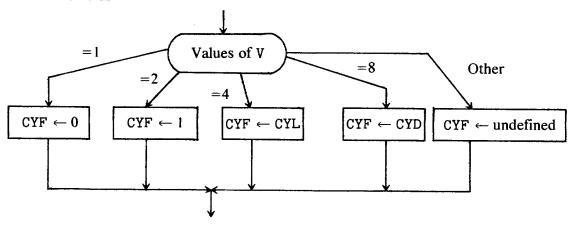

The two registers X and Y are inputs to a 24-bit function box whose combinational logic provides a variety of arithmetic and logical results as output. These results are available in a block of nine 24-bit "result" registers, one machine cycle (167 nanoseconds) after a new value is assigned to either X or Y. The registers, whose meaning is given below, are shown in Figure 3.8.

The length of each result is controlled by the value assigned to our old friend, the CPL register. A value of  $m \le 24$  in CPL allows m-bit results to appear in each result register. For example, if CPL = 7, then only the low-order 7 bits of the results appear in the result registers. [The high-order portion of the result register is padded with zeros.] Thus if X contains the binary number  $100010_2$  and Y contains the binary number  $100010_2$ , and if CPL = 4, then MSKX (masked copy of X) contains the binary number  $10_2$  and MSKY contains  $101_2$ . At the same time, SUM contains  $111_2$ , XORY contains  $111_2$ , etc. All bits to the left of the fourth bit are then zero in each result register. So by controlling the value in CPL, the microprogrammer can generate results of any length up to 24 bits.

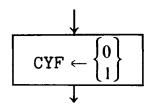

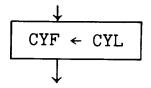

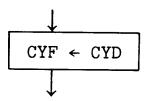

Carries for sums and borrows for differences are indicated in separate, one-bit result registers, CYL and CYD respectively. These carry-out registers may be tested as a basis of an (IF) selection step. Carry values may also be copied into the carry-in flipflop register CYF for input to the

Figure 3.8. Additional registers for data examination and manipulation.

function box on a next sum or difference of X and Y, as might be required, say, in simulating a multiple-precision add or subtract.

# 3.2.2 Arithmetic tidbits

To do a multiply or a divide, one is forced to use a microcoded subroutine built on repeated adds or repeated subtracts. There is, of

course, no floating-point arithmetic primitive in the B1726, so this too must be microprogrammed.

Adds and subtracts can be performed in binary or in 4-bit decimal. In 4-bit decimal arithmetic, each 4-bit subfield of the operands X and Y and of the results in the SUM and DIFF registers is binary-coded 0 through 9.

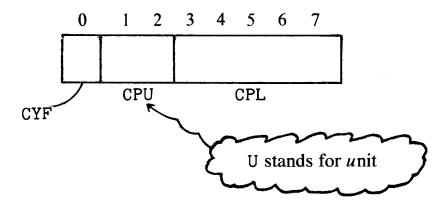

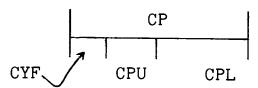

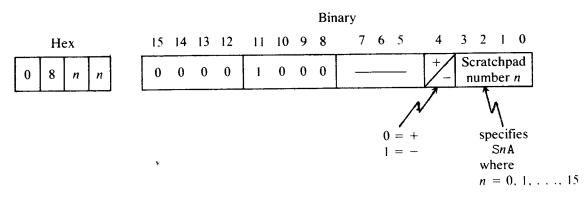

What determines whether X- and Y-registers will be regarded by the hardware as binary or as 4-bit decimal? There is a special 2-bit register called CPU, whose value controls this arithmetic interpretation of X and Y. The CPU is a companion or "cellmate" of the CPL register, both being housed, along with the carry-in flipflop CYF, in the 8-bit CP (control parallel) register.

The microprogrammer can, of course, also set or test the value in CPU and hence can cause the controls to switch back and forth from decimal to binary arithmetic for the results he wants.

Taking stock, the CP register plays an important role in control of arithmetic and (to a lesser extent) of logical operations resulting from the inputs X, Y, and CYF. The subregister CPL controls the length of each result, and the subregister CPU controls the unit (binary or 4-bit decimal) on which arithmetic will be performed. For an overview of the data examination and manipulation capabilities based on the receiver registers X, Y, L, and T, we have now said enough.

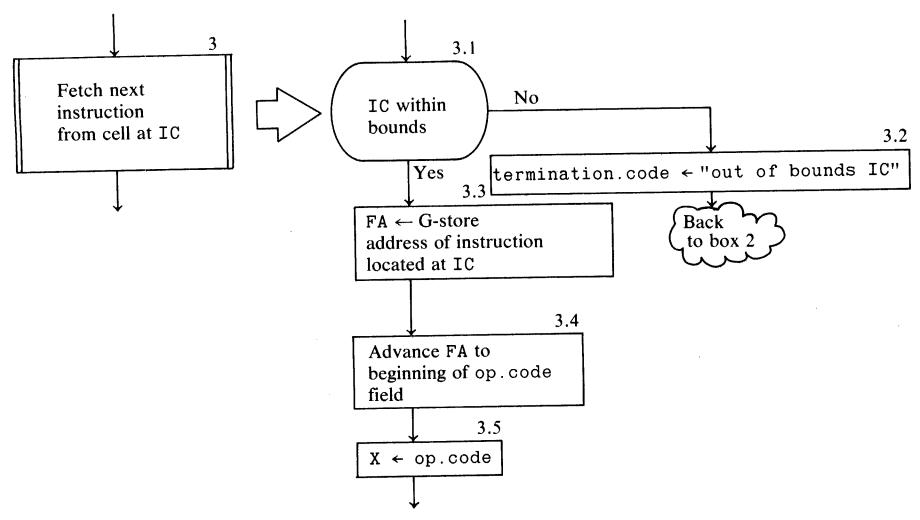

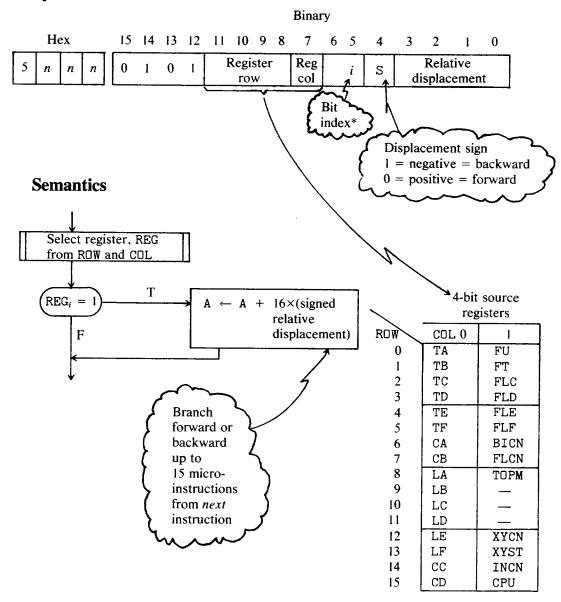

#### 3.3 INSTRUCTION DECODING

At the risk of oversimplification, we can say that a machine instruction consists of an op-code followed by several operands (none, one, or more). If this is true for the machine that is to be interpreted by the B1726 host, then instruction decoding can be thought of as consisting of these steps:

1. Determine, by examination of the op-code field, which microcoded subroutine must be called to carry out the intent of that instruction. (We will call it the "operator subroutine".)

- 2. Evaluate each operand on the basis of the information in each operand field.

- 3. Call the operator subroutine determined in step 1.

If step 2 has been executed before step 3, then the operator subroutine is in effect supplied arguments which are the results produced in step 2. However, if steps 2 and 3 are interchanged, then the operator subroutine must be "smart" enough to know how each operand is to be found and evaluated so as to execute the intended semantics of the operator.

In simple (i.e., regular) machines, not only is there a fixed (or at least small) number of operands for each instruction, but each operand has a simple interpretation. For example, in SAMOS each operand may be regarded as atomic (no substructure) and is a number representing a location in the SAMOS store. For such simple machines it is probably of small consequence (except for limited efficiency tradeoffs) whether or not step 2 precedes step 3.

When operands differ in description according to the statement types in which they appear, as in the case of higher-level (more exotic) machine like FORTRAN, there is greater justification for the interpreter designer to delegate to each operator subroutine the job of deciding how its associated operands are to be fetched or stored. Thus, each operand in a FORTRAN-like machine would probably have several components, such as its *type*, in what *table* (work space) the cell for this operand may be found, the *offset* within this table, and the *length* of the operand. For the remainder of this discussion we wish to keep things simple, so we'll assume we are dealing with a regular machine in which it is quite feasible to execute step 2 before step 3.

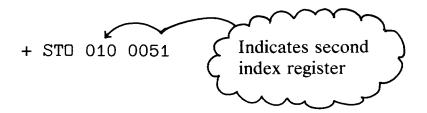

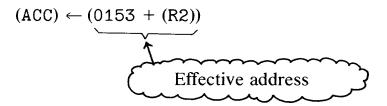

With this case in mind, and without loss of too much generality, we can further narrow the discussion to the case of a one-address machine like SAMOS. For such a machine there are typically, at most, three fields following the op-code field, e.g., operand, index register indicator, and possibly an indirect address indicator. The order is immaterial. Since each field is in a fixed position within the instruction, it is a relatively easy matter to write microinstructions which fetch the "next" instruction from G-store and extract each of its fields. The T-register is ideally suited for this. If the instruction is greater than 24 bits in width, several fetches will be needed, and more of the "local registers" such as L or even X and Y might be used. As each operand is isolated it can be evaluated and its value saved in an agreed-upon scratchpad register.

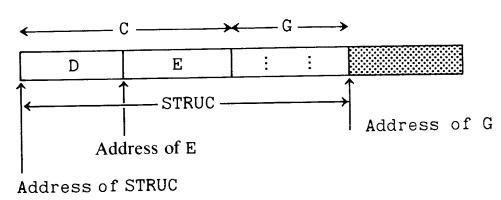

What do we mean by evaluation of an operand? Take the case where we are simulating a machine M whose storage consists of r cells, each s bits wide. We assume that the storage for M ( $r \times s$  bits) will have been allocated in G-store beginning at some absolute address, represented (say) by the symbol B. Then evaluating an operand whose value is (say)

v amounts to a mapping from v to an absolute address in G-store. In this case it is

$$map(v) = B + s \times v$$

where  $0 \le v \le r$ . Of course, the word width s is a constant for machine M. Moreover, B is fixed for a particular interpretation of a program for M. B is based on the contents of the B1726 base register BR.<sup>3</sup> [It may be useful to let the value of r be a parameter of the interpreter so that the storage size of M can be specified anew on each simulation.]

The sequence of microinstructions which performs this mapping must therefore know where to find B, probably s, and r. Very likely B will be found in an agreed-upon scratchpad register.

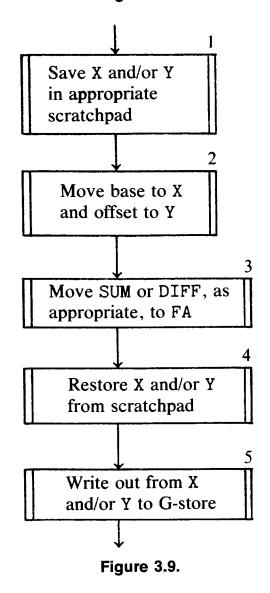

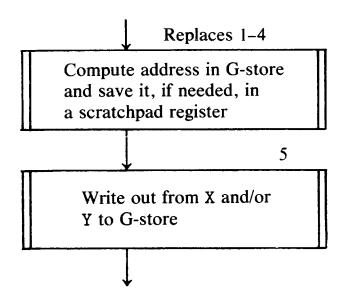

Must address arithmetic of the type required in computing map(v) be performed entirely by the function box? If so, there could be some congestion-induced overhead in the use of registers X and Y. If one or both of these registers hold data values which are to be written out to G-store at an address which is about to be computed in the function box, then data values in X and Y will have to be moved and may have to be given a "round-trip ride" to and from some available scratchpad while the function box is put to use computing the target address—e.g., as shown in Figure 3.9.

To avoid a lot of this overhead the designers of the B1700 attached a full 24-bit adder to the FA register, making it possible to do the most frequently needed address arithmetic (computing offsets by addition and/or subtraction) outside the function box. One can add to or subtract from FA the value of any of the 16 left half scratchpads' registers (SiA, i = 0, 1, ..., 15). Thus in the instruction sequences

```

MOVE BR TO FA % MOVE BASE FROM BR TO FA ADD S7A TO FA MOVE FA TO S9A

```

or

```

MOVE S10A TO FA % MOVE BASE FROM S10A TO FA SUBTRACT S11A FROM FA MOVE FA TO S15A

```

the FA register plays the role of a conventional accumulator (with addend or subtrahend addressed from the left half of the scratchpad and with augend or minuend from any register). We see that if address computation only requires computing an offset from some base, then the

<sup>&</sup>lt;sup>3</sup> We assume that BR is fixed in value during the interpretation process, but in a multiprogramming environment it may be that a program's data space may be relocated before its execution is completed, so in fact BR is not strictly a constant.

wasteful sequence of 5 steps in Figure 3.9 reduces to

We now suppose that, having computed map(v), this value is stored in another agreed-upon register. The values of other subfields that define the operand, such as the index register indicator, can also be stored in agreed slots. The operator subroutine may then be called and it will know, by convention, where to find the values of its arguments, for instance in scratchpad registers S3, S4, and S5. The mechanics of calling the appropriate operator subroutine and returning from it will be discussed in the next section.

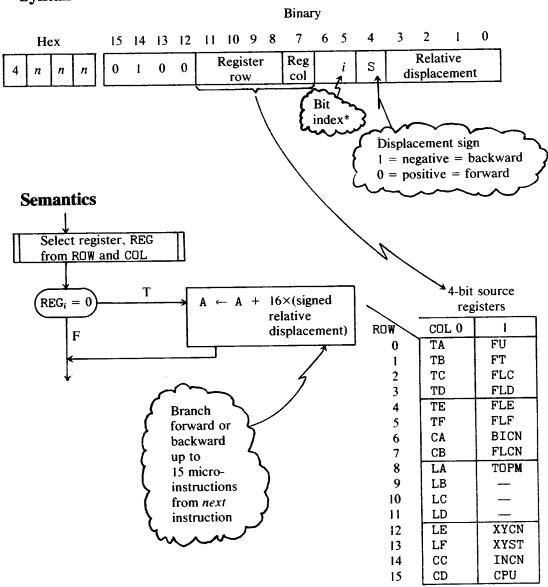

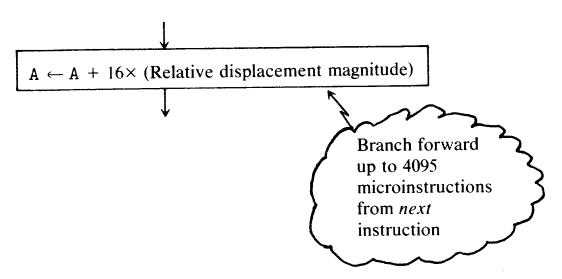

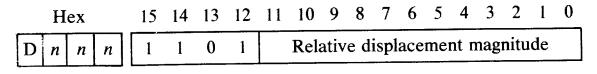

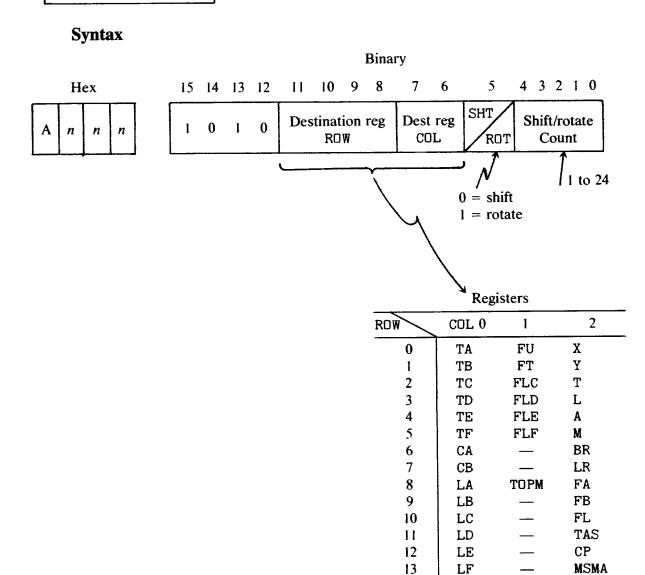

#### 3.4 CONTROL

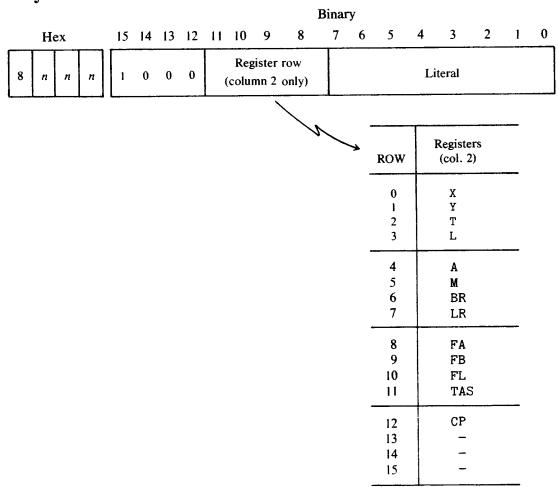

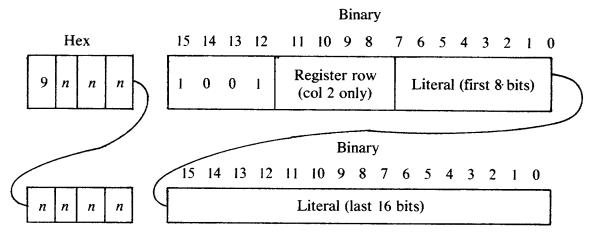

We are now ready to examine more closely the actual control structure of the B1726 microprocessor. Code executed by the B1726 consists of sequences of 16-bit microinstructions. [The machine language of the B1726 is itself a somewhat regular one.] Microcode is regarded as *invariant*, i.e., it shouldn't be altered as a result of being used (interpreted).

To the extent possible, microcode is kept in a separate program store (H-store), whose mode of access is primarily read-only, and where microinstructions are relatively well protected against being accidentally clobbered. Of course the program store has to be loaded periodically with new batches of microcode, so the program store (usually referred to in the literature as *control store*) must also be (and is) writeable. [In fact, there are several ways to write into control store. Use of the special OVERLAY instruction causes code to be shipped from G-store to H-store, and it is also possible to load microcode into H-store from a console cassette tape or from the console switches.] The control store on the University of Utah B1726 has, for example, a capacity of 2048 microinstructions (4096 bytes).

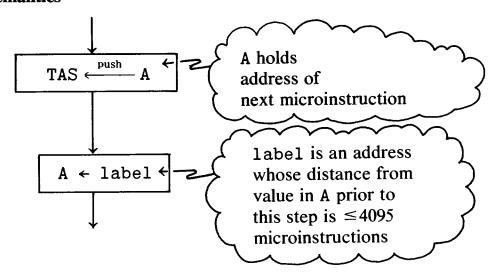

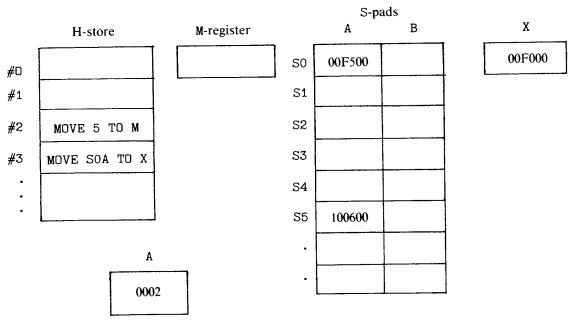

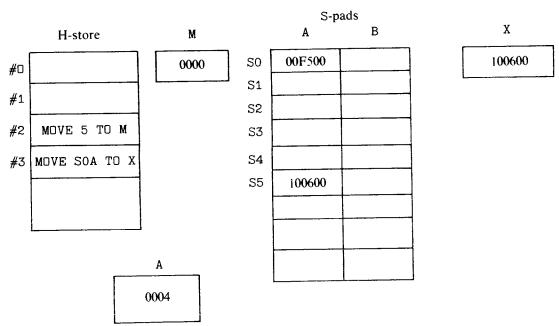

The ordinary cycle for interpreting a microinstruction begins with a fetch from H-store from the location pointed to by the A-register (Figure 3.10), which is the program counter for the hardware. The fetched microinstruction goes to the M-register, whence it is decoded by the hardware for execution.

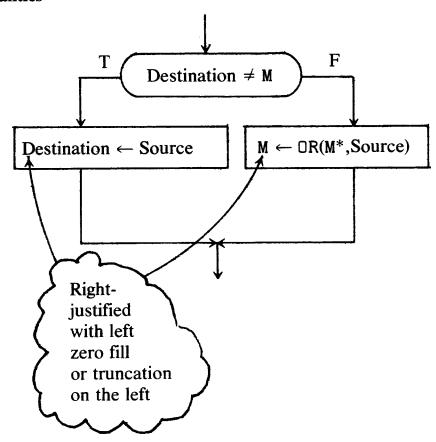

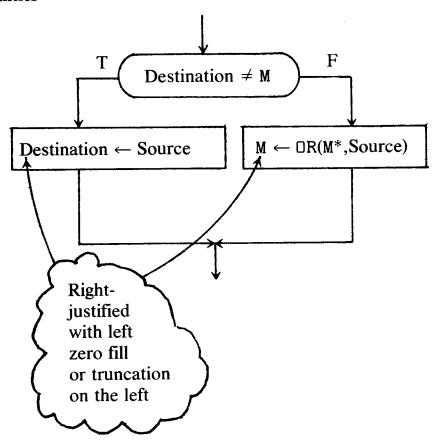

How does the OR box attached to M help us? The actual operation of the hardware in the execution of a B1700 instruction is

- 1. The microinstruction at location (A) is ORed into M.

- 2. A is incremented by 16.

- 3. Instruction in the M-register is decoded, and gates are set appropriately for execution.

- 4. M is cleared (preparatory for next instruction).

- 5. The instruction is executed.

Figure 3.10. Additional registers for control, i.e., interpretation of microinstructions.

Of course, before the very first instruction of a program is executed, the M register must be cleared. This always happens during the initial startup procedure. Suppose that some instruction caused data to be moved to the M register—for example, MOVE 3 TO M. During step 5 the value specified (3 in this case) would be moved to M and would then "participate" in step 1 of the next instruction cycle. Hence the value moved to M can control (modify) the effect of the next instruction. Note several things about this modification.

1. Logical ORing of all 16 bits allows modification of any field of a B1700 operation.

- 2. The effect lasts only for one instruction execution.

- 3. The actual H-store is not changed in any way.

Example Suppose scratchpad registers S12A, S13A, S14A, and S15A contain a list of 4 possible offsets to a base address of a list in G-store. Further, assume we know that TA has a value in the range 0 through 3 inclusive, corresponding to one of the offsets found in S12, S13, S14, or S15. We would like to use the scratchpad ADD instruction to add the offset from the desired scratchpad into FA. The following sequence of microinstructions accomplishes this objective.

MOVE TA TO M ADD S12A TO FA

The scratchpad ADD instruction names S12A as the source, but the address field designating S12A will be DRed with a copy of TA previously moved to M, producing an "effective address" that designates the desired scratchpad register: S12A for TA=0, S13A for TA=1, S14A for TA=2, or S15A for TA=3.

[Warning: We must be careful in the use of the ORing feature, or we may get unexpected results. For example, what is the effect of MOVE TA TO M in the following sequence when TA is again assumed to have a value in the range 0 through 3?

MOVE TA TO M ADD S11A TO FA

[Answer: No effect. Why?]

Another important application of the ORing property of M is in achieving a multiway branch, using a "jump table". For example, suppose we wish to decode a 3-bit op-code to achieve an 8-way branch to one of 8 operator subroutines. Assume that 3-bit op-code is located in bit positions 5 through 7 of the T-register. Then the following instruction sequence would do the trick.

EXTRACT 3 BITS FROM T (5) TO L MOVE L TO M

JUMP FORWARD

GO TO ROUTINE1

GO TO ROUTINE2

:

GO TO ROUTINE7

GO TO ROUTINE8

Explanation First we take advantage of the EXTRACT instruction to

pull out of T a copy of the 3-bit field and move it to another receiver register L. The value moved to L will be padded with high-order zeros. This value is then moved to M.

The JUMP is an unconditional branch whose operand is a signed displacement, e.g., JUMP to "here" +5 or JUMP to "here" -10, where "here" is the current contents of the A-register, now pointing at the next instruction. The special JUMP FORWARD option means JUMP to "here" +0. But we have ORed into this instruction an unsigned integer in the range 0 through 7, so we will have an effective JUMP to one of the eight succeeding instructions, each being a GO TO to a different operator subroutine.

Note that in no case where we take advantage of the ORing feature of the M-register, do we in any way alter the instruction residing in H-store. This ORing feature permits, in a limited way, the instruction modification capabilities made possible in more conventional machines using *index registers*.

Besides indexed JUMPs, of course, we can have arbitrary jumps limited only to displacements (+ or -) of no greater than 4096. In the MIL symbolic language the usual form of such an instruction is

#### GO TO label

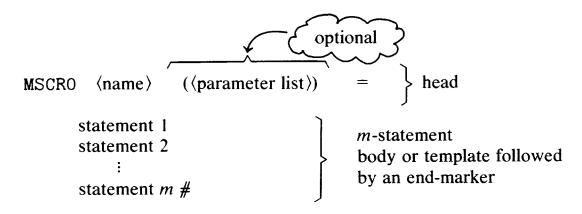

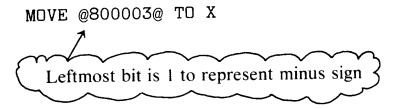

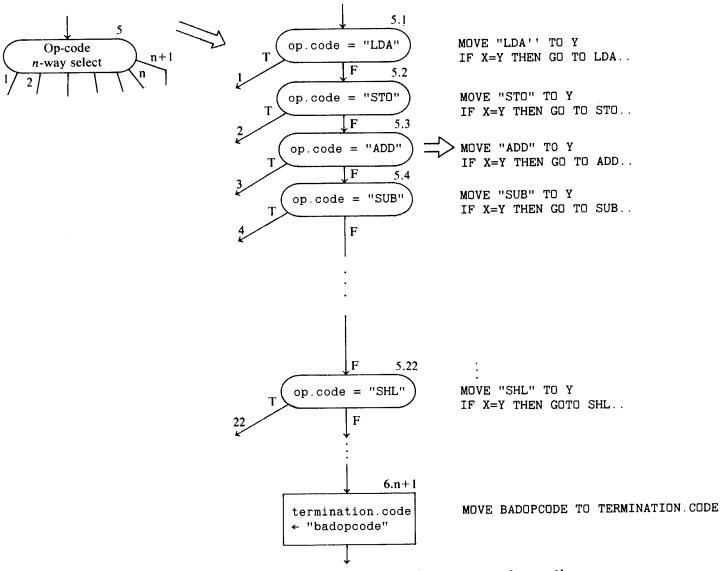

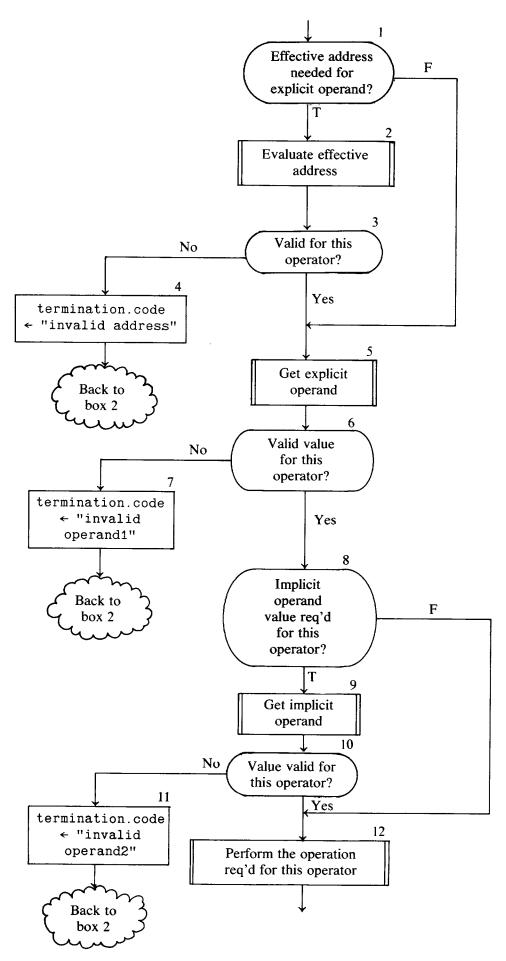

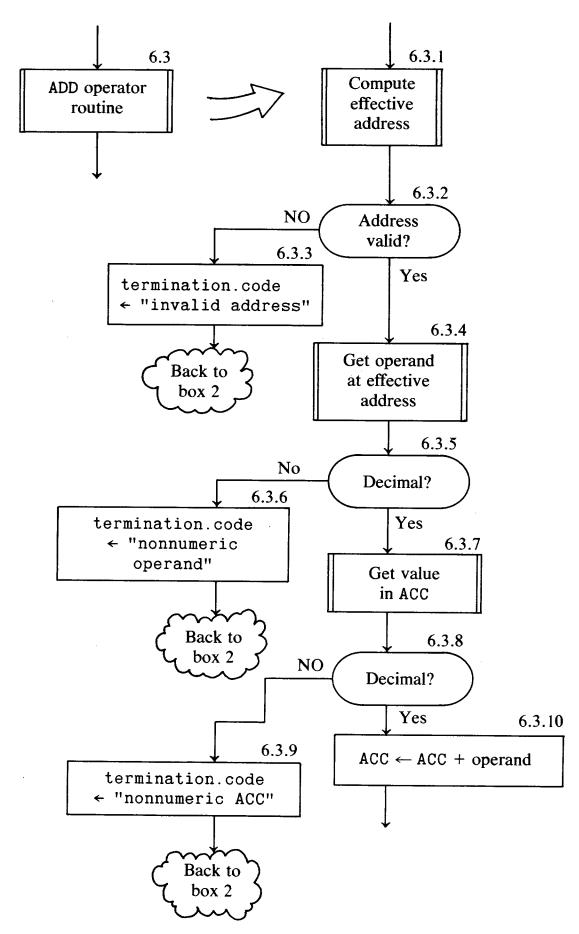

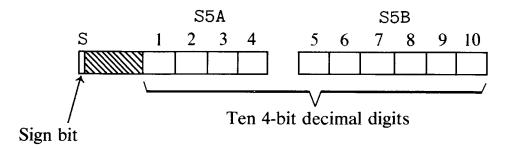

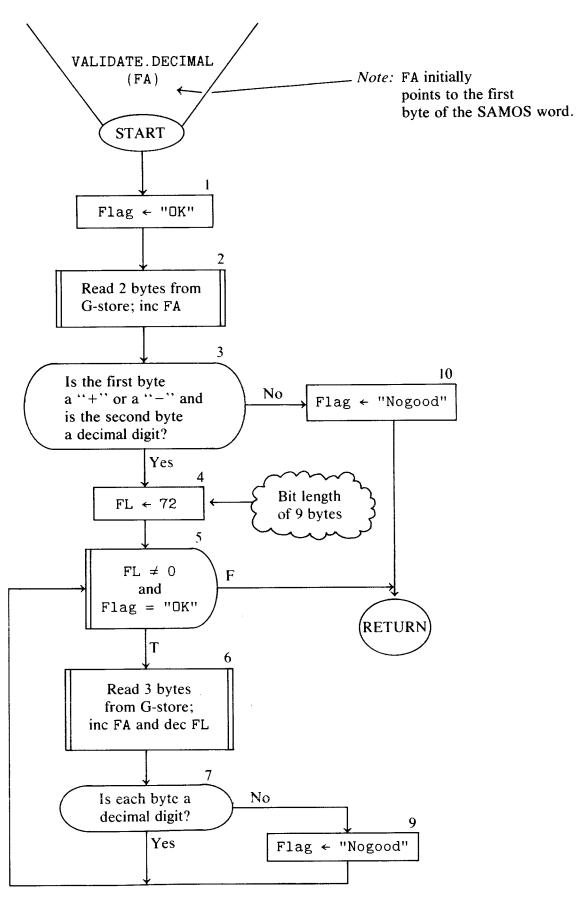

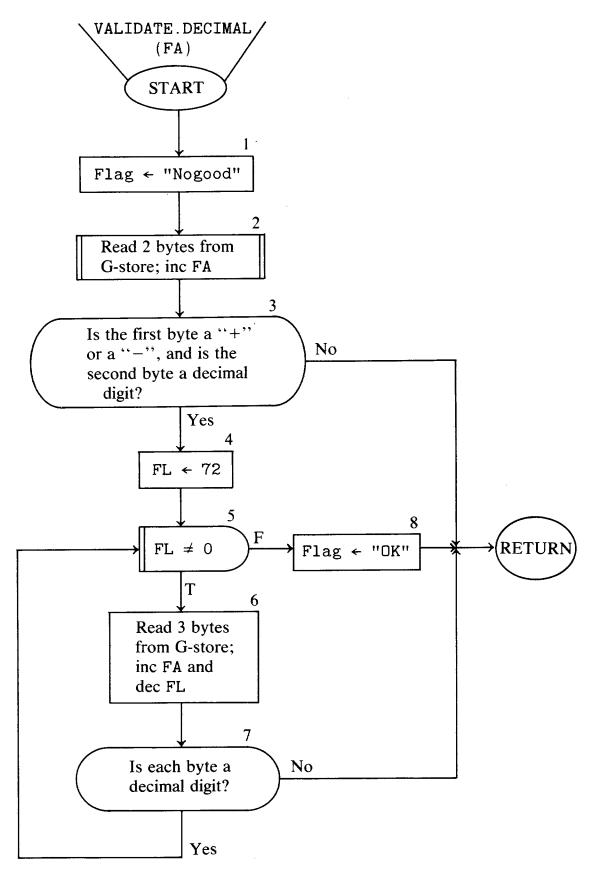

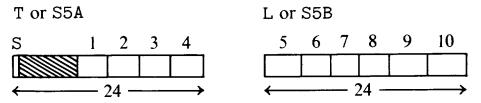

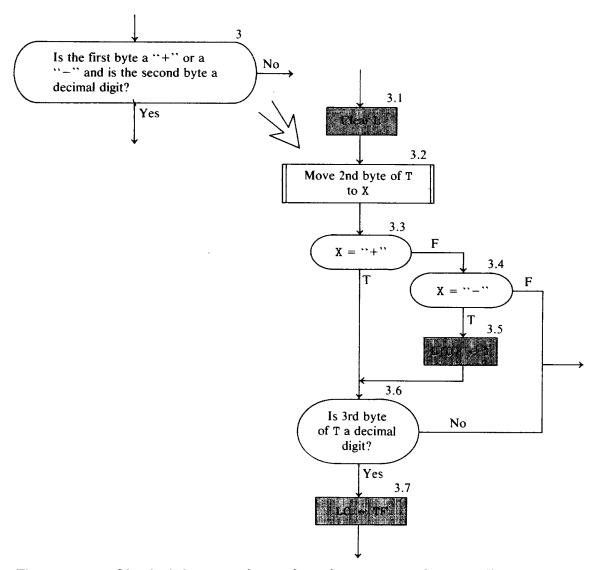

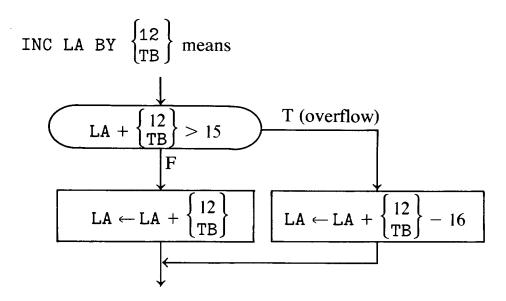

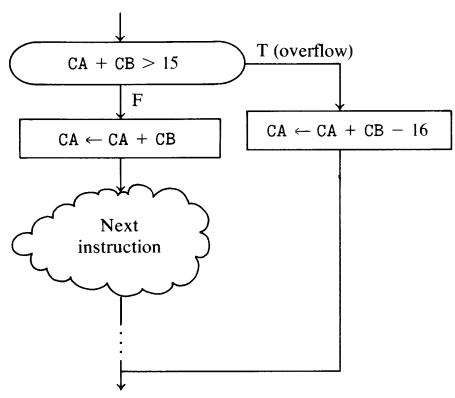

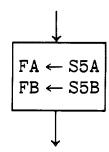

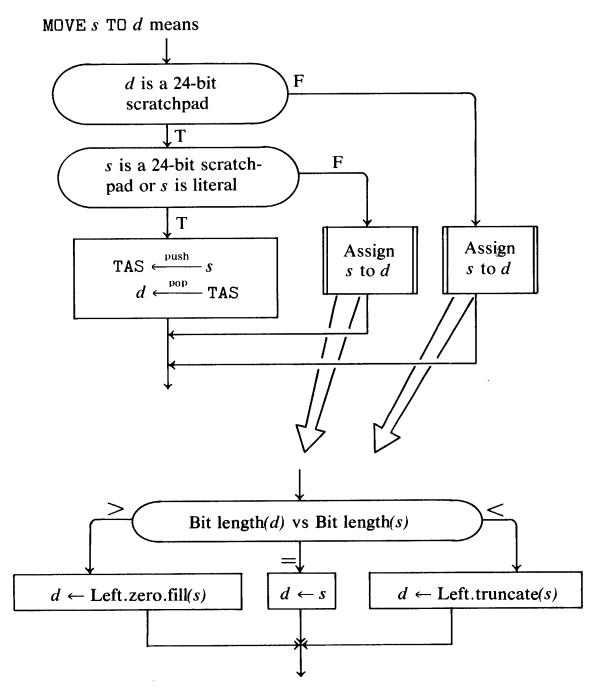

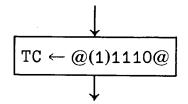

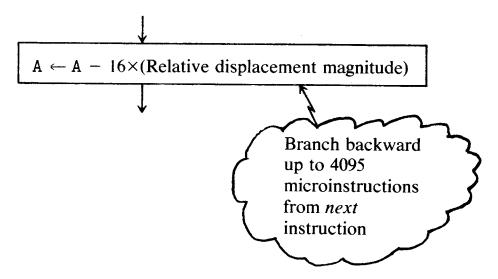

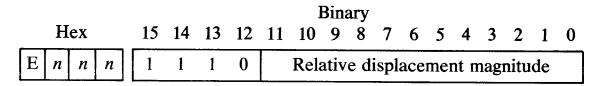

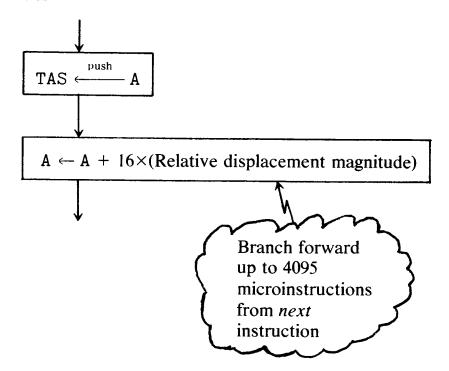

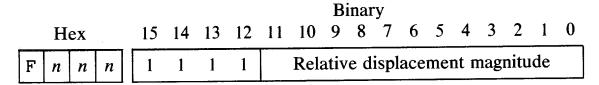

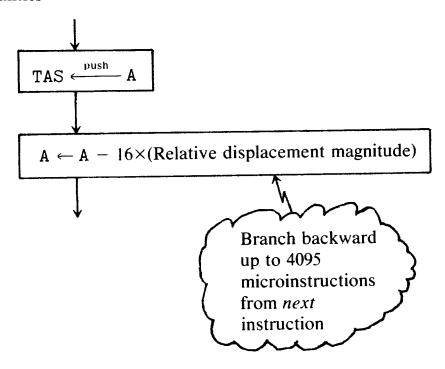

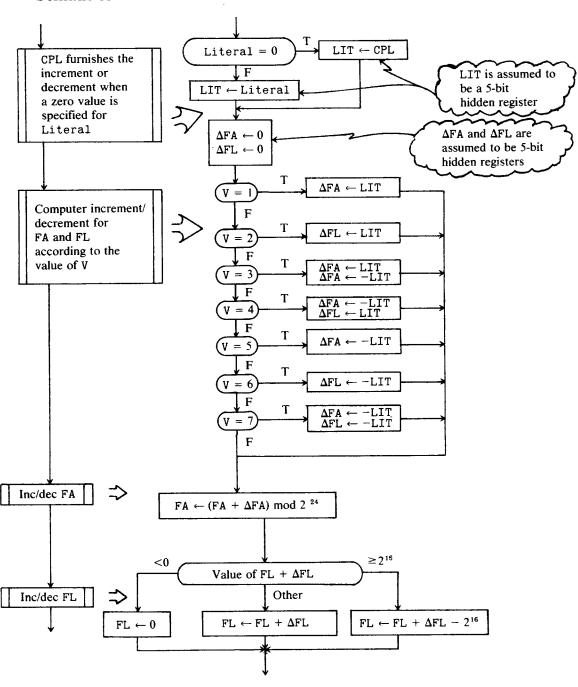

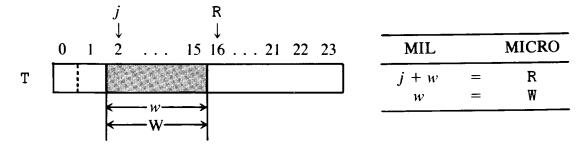

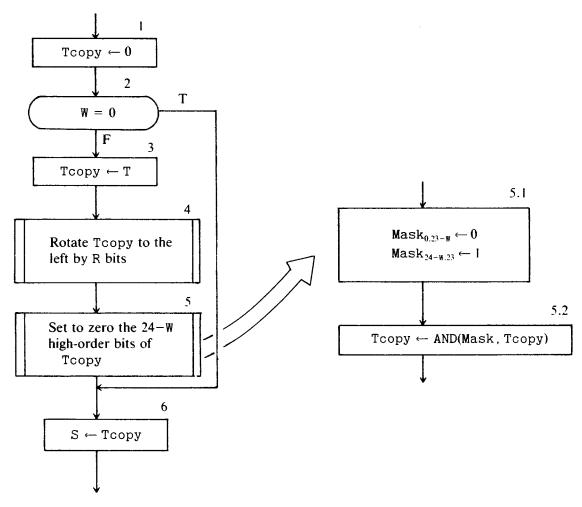

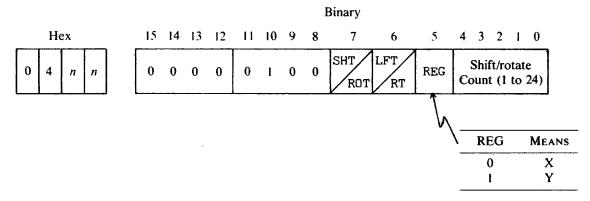

which is converted by the MIL assembler into a jump instruction with an appropriate displacement.