# ARITHMETIC OPERATIONS IN DIGITAL COMPUTERS

## R. K. RICHARDS, Ph.D.

Development Engineer International Business Machines Corporation

### D. VAN NOSTRAND COMPANY, INC.

PRINCETON, NEW JERSEY

**TORONTO**

LONDON

NEW YORK

#### D. VAN NOSTRAND COMPANY, INC.

120 Alexander St., Princeton, New Jersey 257 Fourth Avenue, New York 10, New York 25 Hollinger Rd., Toronto 16, Canada Macmillan & Co., Ltd., St. Martin's St., London, W.C. 2, England

All correspondence should be addressed to the principal office of the company at Princeton, N. J.

COPYRIGHT, 1955, BY

D. VAN NOSTRAND COMPANY, INC.

Published simultaneously in Canada by D. Van Nostrand Company (Canada), Ltd.

All rights reserved. This book, or any parts thereof, may not be reproduced in any form without written permission from the author and the publisher.

Library of Congress Catalog Card No. 55-6234

First Printing February 1955

Second (Prepublication) Printing February 1955

Third Printing August 1955

Fourth Printing February 1956

#### **PREFACE**

Among the first things that are learned in a study of mathematics are rules and procedures for performing basic arithmetic operations, notably addition, subtraction, multiplication, and division. The rules and procedures taught in school are, for the most part, aimed at making the operations as simple and speedy as possible when a pencil and a piece of paper are the only tools. In the design of more elaborate arithmetical tools, it is usually found necessary or at least highly desirable to devise new methods for executing the various arithmetic operations.

This text has been written to point out the shortcomings of pencil-and-paper rules and procedures when applied to computing machinery and to explain the more important of the schemes which have been worked out for executing arithmetic operations in that class of machinery generally known as "digital computers." Of course, to appreciate the features of the different schemes, many other points must be considered, and these range all the way from the systems of symbols which are to be used to the ideas involved in causing a computer to proceed through a long sequence of arithmetic operations in an automatic fashion. In other words, it might be said that the text has been prepared as an answer to the question: "How does a digital computer work?"

In the design of computers, not only the methods of performing arithmetic operations, but also the fundamental concepts with regard to symbolic representation of quantities have been subjected to critical review. For this reason, the explanation of computer functioning has been started with a discussion of systems of symbols which have been invented for representing the numbers entering into the computations. Relatively little attention is given to actual components, circuits, and other engineering details which must be considered when designing a computer. However, these details have been a great influence in the selection of the arithmetic methods to be presented, and the advantages and disadvantages of the various schemes from an engineering standpoint are pointed out throughout the text. Most of the means for performing arithmetic operations are explained through the use of "functional block diagrams," where it is understood that any set of physical components which pro-

iv Preface

vide the indicated functions may be used. A Boolean algebra notation is introduced at any early point and is widely used as a convenient means of representing the block diagrams and, in many cases, as a device for finding improved functional arrangements.

In the descriptions of the arithmetic operations themselves, separate chapters are devoted to the methods employed in the binary and the decimal systems. This separation has been made because, from a machine standpoint, the operations are quite different in spite of the fact that the systems are alike, from a mathematical standpoint, except for a change in the value of the radix. On the other hand, most of the important ideas relating to the organization of a computer and to the programming of it to execute a long series of arithmetic operations are not related to its binary or decimal nature. Since principles of operation have been considered to be of first importance, no attempt has been made to give a complete, detailed description of any one machine, although in some cases the explanations have been patterned after certain machines which seemed to be typical of a category. To explain programming principles, a simplified "specimen" machine was used as a model. By this means it is possible to illustrate the important concepts of programming without the need for describing numerous details which, although highly desirable in an actual machine, tend to cause confusion in explanations and which may be totally different from one machine to the next.

This book was originally prepared as a set of notes to be used with a course of instruction for engineers at IBM's laboratories. I wish to thank all of those at IBM, particularly the students in the classes, who have given assistance either through discussions or through suggesting improvements in the text. Also, I wish to acknowledge with thanks the support and encouragement given me in this project by Mr. Ralph L. Palmer, Director of Engineering at IBM.

R. K. R.

#### **CONTENTS**

| CHAP | TER                                            | PAGE        |

|------|------------------------------------------------|-------------|

|      | Preface                                        | iii         |

| 1    | Symbolic Representation of Quantities          | 1           |

| 2    | BOOLEAN ALGEBRA APPLIED TO COMPUTER COMPONENTS | 26          |

| 3    | Switching Networks                             | 51          |

| 4    | BINARY ADDITION AND SUBTRACTION                | 81          |

| 5    | BINARY MULTIPLICATION AND DIVISION             | 136         |

| 6    | DECIMAL CODES                                  | 177         |

| 7    | Counting, Binary and Decimal                   | 193         |

| 8    | DECIMAL ADDITION AND SUBTRACTION               | 209         |

| 9    | DECIMAL MULTIPLICATION AND DIVISION            | 247         |

| 10   | MISCELLANEOUS OPERATIONS                       | 286         |

| 11   | COMPUTER ORGANIZATION AND CONTROL              | 314         |

| 12   | Programming                                    | 354         |

|      | Bibliography                                   | 385         |

|      | INDEX                                          | <b>3</b> 95 |

## Chapter 1

#### SYMBOLIC REPRESENTATION OF QUANTITIES

To those familiar with ordinary arithmetic processes, the symbols which should be used to represent various quantities may appear to offer no problems or even no room for choice. The Arabic numerals together with decimal points, plus and minus signs, exponents, and so on, serve very well for grade-school arithmetic and higher mathematics as well, and there is no self-evident reason why these same symbols cannot be adopted for use in computing machinery. To some extent these symbols can be used; and, since they are so well established, it is desirable that they be used as much as possible. However, it could hardly be expected that a system of symbols which was developed along with pencil-andpaper arithmetic would be the most desirable system when transported to the field of machine computations. There are many problems connected with the use of the decimal system in a computer, especially when attempts are made to employ it in the arithmetic unit, or that portion of the machine which performs the actual computations. It is because of these problems that it is usually desirable to modify the decimal system, sometimes considerably, in order to adapt the computations to machine operations. In some cases it has been found expedient to abandon the decimal entirely in the computer in favor of another system, known as the binary system, which will be described in detail later.

The increase in speed of computations (other factors assumed equal) and the saving in tubes, relays, and other components that can be achieved by the proper choice of symbols are well known to machine designers. Of equal importance is the fact that mathematical progress can be aided or hindered in no small way simply by the properties of the systems of symbols in use by the mathematicians. The Roman numeral system, for example, did much to stall the Romans in their mathematical endeavors. As another example, Leibnitz and his associates on the Continent for a time far outdistanced Newton and his associates

ciates in England in the development of the calculus largely because the English employed a clumsy system of symbols, while the Germans had a more useful means for expressing the operations and ideas involved.

The best system of symbols which may be used for computing machinery applications is difficult, if not impossible, to determine conclusively. Further, it is probably true that the system which is most appropriate for a computer designed for one purpose can be quite unsatisfactory when applied to a computer designed for another purpose. However, it is possible to point out the features and characteristics of the various systems, and this will be done through relating the symbols to the quantities which they represent. Although a reasonably broad coverage of the symbols available for use in computors is presented, it would be well to keep in mind that further modifications or even completely new systems may be invented which will greatly enlarge the usefulness of computing machinery.

Zero. One of the simplest and most elementary quantities which requires a symbol is the quantity of nothing at all, or zero. A common symbol for zero is 0, which may be thought of as representing a hole or empty container. Everyone who is familiar with the Arabic numerals is familiar with the symbol 0 and it may appear ridiculously trivial to mention it here. When discussing computers, however, it is not a trivial point, because, as a matter of fact, 0 is for some applications an inconvenient symbol to use, and other symbols are frequently adopted. One such other symbol is 999999, and another is 0011. The reasons behind the adoption of such symbols are varied, and they depend to a large extent upon the nature and purpose of the particular computer under consideration. Factors such as reliability of operation, ability to detect errors once they occur, savings in components, to name a few, create problems in the design of computers which are quite different from those occurring when the familiar pencil-and-paper method of computation is employed. One unexpected reason for the adoption of an unusual symbol for zero is that, when this symbol is employed in the internal mechanism of the computer, it is actually easier to cause the computer to print the familiar symbol than when the familiar symbol is used throughout. The details of this and other reasons can be made understandable only after certain other topics have been discussed.

One. A single item or unity is called one and may be represented by the symbol 1, which could easily have been derived from a finger or a stick or some similar object used for counting. As in the case of zero, the symbol for one may be, and is frequently, modified to suit the requirements of the machine. These modifications, incidentally, are not merely the substitution of a character of one shape for the character of another

shape. The shape of the symbol as written on a piece of paper is of no consequence to a machine because the machines do not handle printed information, except in that portion which prints the final result, and in this printing mechanism the type face may have any desired design without the slightest effect on the computations. If data were entered into the machine in printed form, symbols of some shapes could probably be distinguished and identified more readily than those of other shapes; but in all existing machines the input is of some other nature such as punched cards or magnetic tape. The modifications which are of consequence involve the number of characters, the meaning of each character in the group, and its position in the group.

Two. In choosing a symbol for one plus one, or two, there are three quite different lines of procedure that may be followed.

Probably to a person inventing his own system of symbols the most obvious choice for two is two 1's placed side by side. In examining the systems of ancient peoples it is found that this choice is actually rather common. The Roman numeral system, which is well-known even today, employs this notation for two. As has already been mentioned, Roman numerals are clumsy and awkward, and computations performed with them are much more difficult than those performed with Arabic numerals. It is for this reason that Arabic numerals have replaced Roman numerals in all but simple counting applications, such as the designation of the volumes in a series of books or the recording of the date on the cornerstone of a building. It is debatable, though, that the clumsiness in the Roman numeral system is caused by their choice of a symbol for two. The real difficulties are created by their choice for larger numbers, and the possibility of devising a system useful for computers and based on the use of two 1's for two should not be overlooked, although as yet no such useful system is known.

Another choice for a symbol for two is simply a character of a shape different from 0 or 1. The Arabic numeral 2 is an example of such a choice.

A third idea for the development of a symbol for two is to use the same symbols that were employed for zero and one but to place them in such a manner that their meaning is two. A scheme which has received considerable use and which is based on this idea is to use the symbol 1 for two as well as for one but to place the 1 in a different position when it is indicating two. Then, to indicate that the one is in this different position, it is customary to place a zero in the original position. The binary system of numbers is a continuation of this method of notation.

Three and Larger Integers. No outstanding new ideas that could not have been employed for zero, one, and two are obvious for the designa-

#### 4 Arithmetic Operations in Digital Computers

tion of three and larger integers. Three may be symbolized by three 1's, a new symbol such as 3, or by a 1 in the different position combined with a 1 in the original position with the meaning of two plus one. If a 1 in the different position were to be interpreted as indicating three, a 0 would be placed in the original position; the ternary system of numbers involves this step in its system of symbols.

For integers larger than three, all of the processes just described may be extended, but the writing of a large number of 1's or the establishment of a great many different symbols to represent large numbers is clearly impractical. Although each of these two systems is by itself impractical for large numbers, a combination of the two systems is not at all out of the question. For example, symbols may be established for one, ten, one hundred, one thousand, and so on, and any reasonable integer could be represented by a reasonable number of these symbols written in any sequence or relative position. No particularly successful system is known which is based on this combination, however. The Roman numeral system is similar but with additional complications.

The greatest advances in arithmetic have been made through the employment of a very few different symbols with their position being used to indicate their value. The ten familiar Arabic numerals 0 through 9 employed in the well-known manner comprise the most outstanding system of this type.

Radix. The number of digit symbols employed in a system such as the Arabic numeral system is called the radix of the system. Consideration of various number systems, particularly when the consideration has been for possible use in digital computing machinery, has been largely limited to systems of the Arabic numeral type but with a variation in the choice of The selection of radix ten was made long before the conception of computing machinery and was probably chosen to facilitate counting on fingers. When chosen for such a reason, radix ten is a good choice. But when finger counting is not practiced, some other radix might appear more attractive. The advantages of radix twelve have been extolled from time to time, and this radix has actually been adopted in a limited way for use with time clocks and in the counting of eggs, tacks, and other objects by the dozen and gross. The advantages of twelve are derived mainly from the fact that twelve is divisible by more numbers than any other small integer. In the design of computing machinery, twelve has no outstanding advantages over ten. However, certain other radices do offer substantial advantages over ten for use in computing machinery when the machinery is designed along certain lines. The phrase, "when the computing machinery is designed along certain lines," is important, because there are ways of going about designing a computer for which radices eight, ten, or eleven, for example, would be approximately equally desirable. For those designs where the radix does make an important difference, radices two, eight, and sixteen offer the best possibilities for an efficient computer. Actually, radix two is the only one which has been found to offer any improvements functionally. Radices eight and sixteen are mentioned because they can be employed with substantially the same designs as used for two. In such cases they amount to little more than an imaginary grouping of the radix two or binary digits except for printed representations of the data and the results. Printed numbers in the binary system are undesirable because it is difficult to handle a large number of nothing but 0's and 1's without making excessive errors.

So far as is known, radices two, three, eight, ten, twelve, and sixteen are the only ones which have ever received serious consideration for use in computing machinery. The list of those which have actually been used is much more restricted. In fact, no computer is known in which a radix other than two or ten is employed. One minor exception to this last statement exists in that at least two companies have built small electromechanical desk computers in which radix eight is used. The purpose of these radix eight computers is to provide a more satisfactory means for manually checking the computations performed on the radix two computers; therefore, it would not be quite correct to consider them in the same category.

The terms binary, ternary, and decimal have already been mentioned as referring to systems of radix two, three, and ten, respectively. Octonary, duodecimal, and sexadecimal are the accepted terms applying to radix eight, twelve, and sixteen, respectively. It is interesting to note that the Standards Committee of the Institute of Radio Engineers has gone to the trouble of listing the adjectives to be used in describing systems of many other radices, including, for example, septendecimal for seventeen and nonagenary for ninety.

The Digits and Numbers. By way of definition, a digit is a single symbol or character representing an integral quantity. A number is a quantity represented by a group of digits. The usual relationship between the digits,  $d_i$ , and the number, N, may be expressed mathematically as

$$N = d_0 + d_1 R + d_2 R^2 + d_3 R^3 + \cdots$$

where R is the radix (also an integer) of the number system in use. A further condition which is usually, but not necessarily, applied is that the number of digits be equal to the radix and that  $0 \le d_i < R$ .

When applied to computing machinery, another term frequently used

to indicate a group of digits is "word," but the digits in a word may have any of a wide variety of meanings, and there is not necessarily any connection between a word and a quantity.

It is standard practice to write the digits of a number in the opposite order from that shown above; that is,

$$N = \cdots d_3 d_2 d_1 d_0$$

This way, the digits appear from left to right in order of decreasing significance where the significance of a digit refers to the change in N that would be caused by a change in the digit. The term "order" is also used in connection with digit significance, and it means the digit position in the group with high and low orders referring to large and small significance, respectively. The placing of the higher-order digits on the left seems reasonable in view of the practice of reading from left to right, because it is thereby possible to ascertain the relative magnitude of a number at a glance more easily than if the low-order digits were encountered first. Although the arrangement of the digits on a piece of paper is of little consequence, the practice of reading and writing the highest-order digit first in time is sometimes a source of considerable difficulty in the design of computers. The difficulty is especially acute for small computers where the data are sent directly to the arithmetic unit as an operator keys it one digit at a time; and the difficulty arises because it is, in general, awkward to perform computations on numbers where the digits appear in descending order of significance.

A somewhat different requirement often arises in the printing of digits. It is customary to write a number such as 0076, for example, as 76, without any zeros in orders higher than the highest-order nonzero digit. In a computing machine the zeros are not usually nonexistent as may be the marks on a piece of paper, and therefore it is necessary to provide means for suppressing the printing of the unwanted zeros. If the printing is done one digit at a time with the digits in ascending order of significance, the zero suppression function is difficult to incorporate into a machine. but if the digits are printed in descending order of significance, zero suppression is relatively easily accomplished.

The term "significant" has another, slightly different meaning in connection with digits. A digit is significant if it is any of the digits of a number except one of zeros in orders higher than the highest order nonzero digit and if it is known or believed to be of consequence for the accurate representation of the magnitude of the quantity being represented by the number. If, because of round-off errors, inaccuracies in measurement, or otherwise, a digit is believed to be of no consequence for the accurate representation of the magnitude of a quantity, this digit is called "not significant." It usually follows that, if any given digit is not significant because of an inaccuracy, all lower-order digits in the number are also not significant.

It is now almost self-evident that a "digital" computer is a computing device which employs numbers composed of digits to represent the various quantities undergoing the computations. For some computations of purely mathematical interest the numbers or the digits are the end and not just the means, but the functioning of the computer is the same in either case. In a digital computer the individual digits are represented by variations in discrete steps of a different set of physical quantities which may include distance, angle, time, electrical potential, magnetization, and others. The physical quantities undergoing computations are related to the physical quantities in the computer through the medium of digits and numbers, which are symbols used to facilitate the computations in the computer.

There is another class of computing machinery known as "analog" computers, which differ from digital computers in two fundamental respects. The physical quantities in an analog computer are varied continuously instead of in discrete steps, and they are direct representations of the physical quantities undergoing computations rather than representations of intermediate symbols. Since digital computers are the subject of this study, analog computers will not be discussed in more detail.

Economy of Storage "Space" Through Choice of Radix. A factor frequently mentioned in connection with the choice of radix is the amount of equipment necessary to store a given amount of numerical information. This factor is of interest in the design of computers, because it is usually necessary to store, at least temporarily, in the computer itself the numbers making up the input data, results of intermediate computations, and the final results to be printed. In addition, in some computers the "program" for a given problem is stored in the same storage unit with the same system of symbols as other numerical information.

In order to discuss the amount of equipment required to store a number, it is necessary to consider the nature of the equipment. One assumption that may be made is that the amount of equipment required to store one digit is proportional to the radix of the digit. That is, two units of equipment may be required for a binary digit, three for a ternary digit, ten for a decimal digit, etc. In some cases such an assumption is approximately correct. If the storage device is a mechanical wheel, the number of gear teeth or detent positions would be proportional to the radix. Also, it is possible to design electronic storage equipment wherein

#### 8 Arithmetic Operations in Digital Computers

the required number of vacuum tubes is proportional to the number of stable states of the circuit. It is easy to design a circuit employing two triodes which has two stable states and therefore is capable of storing a binary digit, with the existence of the circuit in one state indicating 0 and its existence in the other state indicating 1. It is not difficult to design a circuit employing three triodes which has three stable states for the storage of a ternary digit. The extension of the design to a circuit with ten stable states and employing ten triodes is possible, but such circuits are generally unreliable and not satisfactory. A different approach to the problem may be made by using a number of circuits, each employing two triodes and each with two stable states. For radix ten, then, ten such twin-triode circuits would be employed, and provision would be made to cause one and only one of the circuits to be in a given state of equilibrium at any one time, with all the other circuits in the opposite state of equilibrium. Although twice as many triodes are required (2R, where R is the radix), it is possible to design reliable operating circuits of this type, and the assumption that the amount of equipment required for one digit be proportional to the radix is satisfied.

If n is the number of digits,  $R^n = N$  is a measure of the maximum amount of information the digits can represent and is equal to the number of different stable states of the digit-representing devices considered collectively. With the above assumption, the amount of equipment required to store N is proportional to nR. Both n and R are usually integers so that when a change in radix is made there is also of necessity at least a small change in N. Therefore, an exact comparison of the storage efficiency of the various radices is difficult, but for illustrative purposes it will be assumed that N can be held constant as R is varied. Then,  $n (\log R) = \log N = K$ , where K is a constant. Therefore, the amount of equipment is proportional to  $KR/\log R$ . To determine the most efficient radix for storage, the expression  $R/\log R$  should be examined for minima. By taking the derivative of R/log R with respect to R, it is found that there is a minimum at  $R = e \approx 2.718$ , but the significance of a nonintegral radix is difficult to imagine. A tabulation of the expression for several selected radices is more useful.

| Radix    | R/log R |

|----------|---------|

| <b>2</b> | 6.64    |

| 3        | 6.29    |

| 4        | 6.64    |

| 5        | 7.15    |

| 8        | 8.86    |

| 10       | 10.00   |

| 12       | 11.12   |

| 16       | 13.29   |

The tabulation indicates that radix three is the most efficient, that radices two and four are only slightly less efficient than three, and that radices ten and higher are substantially less efficient.

It should be remembered that these results were obtained after making the rather restrictive assumption that the amount of equipment required to store a digit is proportional to the radix of the digit. Some serious objections may be made to this assumption, because it seldom applies to any practical example. Even in the case of the gear teeth on a storage wheel, it does not apply well. Much more equipment than gear teeth is required to make a complete and useful mechanical storage device. In fact, in this particular case, the additional equipment adds so many complications that a meaningful comparison of radices is almost impossible.

In the case of twin-triode circuits where each circuit has two stable states, a different objection to the assumption may be raised. The objection is that it is not necessary to use, for example, ten such circuits to store a decimal digit, and this is so because each circuit may function independently. Four independent circuits, each with two stable states, are sufficient for the storage of a decimal digit, since the four taken together can exist in any one of  $2^4 = 16$  stable states. Six of the stable states may be disregarded, and the other ten may be used to represent the digit. With a scheme such as this, the inferiority of radix three when compared with radix two is clearly evident. To store a ternary digit through the use of bistable twin-triode circuits, two such circuits are required, and of the four stable states available, three are used and one is wasted. To store a binary digit, only one twin-triode circuit is required, and there is no waste in the stable states. Because there is no waste in the stable states, no radix can be more economical with regard to storage space than radix two when bistable storage elements are used, although any radix that is a power of two may be equally economical provided each individual digit is coded properly. If, for example, three twin-triode circuits are used in the storage of an octonary digit, all possible combinations of stable states must be used in designating all possible values of the octonary digit. In this respect the octonary system is practically ne different from the binary system; the octonary digits may be considered a grouping by threes of the binary digits.

Most of the various types of storage units used in computers are composed of devices which are essentially binary in character, such as the twin-triode circuits just mentioned. Other examples are a hole punched or not punched in a card or tape, a relay which may be open or held closed by the action of a holding coil, a pulse which may be circulating in a delay-line storage unit or which may be nonexistent, a "dot" or a

#### 10 Arithmetic Operations in Digital Computers

"dash" in a Williams type electrostatic storage tube, and magnetization in one direction or the opposite direction in a small area of magnetic tape. One of the few exceptions to the rule is the mechanical counter wheel. Some of the devices mentioned as being binary in character could conceivably be used in decimal fashion such as by using the intensity or direction of magnetization to indicate the magnitude of a decimal digit, but little success has been achieved in making devices of this character reliable.

If one of the essentially binary storage devices is employed, the question arises as to how much saving in storage space may be secured by changing from, say, the decimal system to the binary system. The problem may be solved in the following manner. The number of storage elements, D, necessary to store a decimal number of d digits is D=4d. The maximum number of different conditions, M, that can be represented by this number is  $M=10^d$ . Similarly, the number of storage elements, B, necessary to store a binary number of b binary digits is b=b, and the maximum number of different conditions that can be represented by this binary number is  $b=10^d$ . For a given amount of information to be stored,

$$10^d = 2^b$$

and  $10^{0.25D} = 2^B$

From a solution of this equation it is found that  $B \approx 0.83D$ . In other words, a saving of approximately 17% may be obtained by changing from a decimal system employing four storage elements per digit to a binary system.

To illustrate the above result, consider the storage of a ten-digit decimal number through the use of 40 storage elements. A binary number which is nearly as large,  $2^{33} = 8,589,934,592$ , may be stored through the use of 33 storage elements. The saving is in approximate agreement with the computed result.

It is of interest to solve the problem under the assumption that the amount of storage space is a constant and to compare the amounts of information that may be stored through the use of different radices. For instance, with four storage elements, one out of 10 different conditions may be recorded by employing the decimal system, but one out of 16 different conditions may be recorded by employing the binary system. The increase is 60%. With 32 storage elements, the respective numbers are  $10^8$  and  $2^{32} = 4,294,967,296$ , which indicates an increase of over 4000%. Such a comparison is valid if information is defined as being proportional to the number of possible different stable states, but this definition is not very satisfactory. It is better to define information as

being proportional to the logarithm of the number of different stable states. The reason for the use of the logarithm may be explained through the use of a simple example. Assume that L letters may be written on one page. Since there are 26 letters in the alphabet, the number of different arrangements of the letters (neglecting spaces, periods, etc.) that may appear on one page is  $26^L$ . The number of different arrangements that may appear on two pages considered together is  $26^{2L}$ . The ratio of the logarithms of these two quantities is two, which indicates the generally accepted fact that twice as much information may be written on two pages as may be written on one page. With the latter definition, the ratios of the quantities of information are

$$\frac{\log 10}{\log 16} = \frac{\log 10^8}{\log (4.29) \ 10^9} \simeq 0.83$$

which is in agreement with the result obtained previously.

The 17% saving in storage space which may be achieved through the use of the binary system when compared with the decimal system is probably worth considering, but it is doubtful that a decision on a choice between the two systems has ever turned on this factor. The differences in the nature of the computer components and circuits which may be or must be used with the respective systems are much more striking.

Other Possible Systems of Symbols. Although the Arabic numeral system and similar systems, but with different radix, are the only ones with which much success has been achieved and which have found general use, it might be well to mention certain other systems. Although zero is a logical starting point for a system of numbers, it is not the only possible starting point. In fact, historically, zero was not recognized and understood until long after the positive integers were in common use. Symbols for the positive integers can then be employed in such a fashion that they signify zero. For example, 1-1, with the meaning of one minus one, is a possibility. Another idea which may be employed in the development of a system of symbols is to have certain symbols in a group be multiplied by certain other symbols in the group. An example would be the assigning to 23 the value of two times three, or six. It is easy to let the imagination run wild on a wide assortment of schemes of this nature; but since they have not been found to have any practical value, they will not be discussed in more detail.

A system that deserves slightly more attention is called the "reflected binary" system, its name being derived from a simple method by which it may be generated. The outstanding feature of the reflected binary system is that the representations of successive integers differ, one from

#### 12 Arithmetic Operations in Digital Computers

the next, by only one digit. The system starts with the customary 0 for zero and 1 for one. For two and three, the 0 and 1 are written in inverted sequence and then distinguished from zero and one by a 1 in the second position. Therefore, for zero, one, two, and three, the representations are 00, 01, 11, and 10, respectively. For four through seven, these symbols are repeated, again in inverted sequence, with a 1 in the third position to distinguish them from zero through three. The symbols for eight through fifteen and so on are generated in an analogous manner. A list of the symbols for zero through fifteen is shown below to illustrate the process more clearly.

| $\mathbf{Zero}$  | 0000 | ${f Eight}$       | 1100 |

|------------------|------|-------------------|------|

| One              | 0001 | Nine              | 1101 |

| Two              | 0011 | ${f Ten}$         | 1111 |

| $\mathbf{Three}$ | 0010 | $\mathbf{Eleven}$ | 1110 |

| Four             | 0110 | Twelve            | 1010 |

| Five             | 0111 | Thirteen          | 1011 |

| Six              | 0101 | Fourteen          | 1001 |

| Seven            | 0100 | Fifteen           | 1000 |

Many variations in the above scheme are possible. For one thing, any column of digits may be interchanged with any other column. Actually, it is not difficult to derive such a system by simply changing one digit at a time in an almost random fashion. An example is shown below.

| $\mathbf{Z}$ ero | 0000 | $\operatorname{Eight}$ | 0110 |

|------------------|------|------------------------|------|

| $\mathbf{One}$   | 0001 | Nine                   | 1110 |

| Two              | 0011 | Ten                    | 1111 |

| $\mathbf{Three}$ | 0111 | Eleven                 | 1011 |

| Four             | 0101 | Twelve                 | 1001 |

| Five             | 1101 | Thirteen               | 1000 |

| Six              | 1100 | Fourteen               | 1010 |

| Seven            | 0100 | Fifteen                | 0010 |

A useful application of the reflected binary system or one of its variations is found in some types of analog-to-digital and digital-to-analog conversion equipment. Its advantage is derived from the fact that successive integers differ, one from the next, by only one digit. This property is in contrast with the familiar decimal system and similar systems, because in these systems successive integers may differ by several digits. For example, 3999 and 4000 are successive integers, yet the digits in each of the four orders are different.

Unfortunately, the usefulness of the reflected binary system does not extend to arithmetic operations. Even simple addition is relatively diffi-

cult with the system, and therefore it is not expected that it will find much use in digital computers.

Negative Numbers. Negative numbers are in such common use today that it is somewhat surprising to learn that it was in relatively recent centuries that they were first recognized and understood. Probably, negative numbers were slow in coming into use because there is no such thing as negative material or negative space, at least according to the concepts of classical physics. When a quantity is spoken of as being negative, it invariably can, with a simple alteration of viewpoint, be considered as positive. A temperature of minus 10°C is a positive temperature on the Fahrenheit or Kelvin scales; a negative sum of money usually implies a debt and would appear as a positive sum in the creditor's account books; a dimension tolerance may be listed as plus or minus two-thousands of an inch, but in this case positive or negative indicates direction from a given point and it should not be taken to indicate the existence of negative distance. The scoring system used for certain card games comes closer to the use of true negative quantities, if a score may be considered a quantity. For certain eventualities in the game, a player receives points to be added to his score; but for certain other eventualities, points must be taken away from his score. It may well happen that the player loses more points than he gains, in which case his score becomes negative or "in the hole." Even though examples of true negative quantities are difficult to find, the value of negative numbers for representing the application of a quantity should be apparent. The value of negative numbers becomes considerably more outstanding when computations are performed with numbers representing the quantities.

From a purely mathematical standpoint, there is no reason at all why the series of integers has to have an abrupt ending at zero. Mathematical symobls may be devised to indicate solutions to problems such as 2-5=?, and the relationship, or lack of it, of the symbols to physical quantities may be ignored. The customary way to indicate the solutions to such problems is to extend the series of integers in the opposite direction from zero and to call the new integers minus or negative. Note that the minus sign in the problem means that 5 is to be taken away, that is, subtracted, from 2. The 5 is not by itself a negative number; if it were negative, the problem would have been written some other way, such as 2+(-5)=? The minus sign therefore has two different, although related, meanings. One meaning is the designation of the operation of subtraction, and the other is the designation of those integers which continue the series of integers beyond zero in the direction of smaller numbers. The terms "small" and "large" and also the frequently used

#### 14 Arithmetic Operations in Digital Computers

terms of "less than" and "greater than" are derived from the application of numbers to physical quantities, and although phrases such as "less than nothing" or "smaller than zero" have little meaning when applied to physical quantities, they may assume a useful meaning when applied to negative numbers.

The most familiar system of symbols for negative numbers is the same system which is used for positive numbers, where the group of digits indicates the "distance" from zero, and a sign, plus or minus, indicates the "direction" from zero. It follows that, for a negative number, all coefficients in the expression  $d_0 + d_1R + d_2R^2 \cdots$  are negative. For positive numbers, the plus sign is frequently omitted, with the understanding that the absence of a minus sign signifies that the number under consideration is positive.

From a mathematical point of view, the sign of zero is usually of no consequence and may be either plus or minus, or, in other words, plus zero, minus zero, and zero without any sign indication all refer to the same integer. Nevertheless, it is sometimes desirable to retain the sign of zero in a problem to indicate from which direction the computations proceeded in arriving at the result of zero. For commercial applications, it is customary to consider zero as a positive quantity always; the red ink is not used unless the balance is less than zero. Although they offer no problems with paper-and-pencil computations, the details concerning the sign of zero frequently are a source of considerable annoyance in the design of computing machinery.

A question which arises at this point involves the necessity or desirability of requiring that all coefficients in the expression for a number be positive or all be negative. This requirement is not necessary, although the advantages to be gained by omitting it are not obvious. One result that is obtained by allowing the coefficients to be independent of one another with regard to sign is that a given integer then has no unique representation. For example, another decimal representation for the integer, 7, would be a 1 in the tens order and a -3 in the units order. The representation can be made unique, if desired, by restricting the range of the integers to only ten different values, such as from -4 to 5, and it turns out that there are some practical applications of this idea in connection with decimal multiplication and division.

Another system with positive and negative coefficients which has been studied with at least moderate thoroughness is the ternary system. Instead of using 0, 1, and 2 for coefficients, the coefficients which are used are -1, 0, and +1, abbreviated to -, 0, and +. The nature of the system may be illustrated by listing a few of the integers.

| -3 | 0 - 0 | +4 | 0 + + |

|----|-------|----|-------|

| -2 | 0 - + | +5 | +     |

| -1 | 00 —  | +6 | +-0   |

| 0  | 000   | +7 | +-+   |

| +1 | 00 +  | +8 | +0-   |

| +2 | 0+-   | +9 | +00   |

| +3 | 0 + 0 |    |       |

As can be seen from the brief listing, the sign of the number is contained in the digits making up the number, but since a given nonzero digit always represents a number which is larger in magnitude than the sum of all less significant digits, the sign of the number may be quickly determined from the sign of the most significant nonzero digit. The procedure for inverting the sign of a number while not changing the magnitude is to change all +'s to -'s and all -'s to +'s and to leave the 0's unchanged. Addition and multiplication tables for this system may be built up without difficulty. The multiplication table is particularly simple; and, because of it, the study of the system can be a source of great fascination. Further, it is intriguing to visualize a computer which uses positive electrical pulses to represent +'s, negative pulses for -'s, and no pulses for 0's. However, it takes more than a simple multiplication table and a bare idea about pulses to design a computer. When the difficulties which are encountered in the design of a ternary computer are combined with the dearth of ternary computer components and with the difficulties in adapting the system to applications where the decimal system is already entrenched, it appears that the disadvantages of the ternary system with positive and negative coefficients substantially outweigh the advantages.

There are cases, however, where the simple medium of plus and minus signs is not the most convenient means of indicating negative quantities. Consider a computer that is performing only the function of counting, and assume that it has started with some positive number and is counting downwards or in the direction of smaller numbers. The units counter wheel (or other counting device) proceeds from digit to digit in the sequence of  $\cdots 2$ , 1, 0, 9, 8  $\cdots$  as it counts, and each time it passes from 0 to 9 it causes the tens counterwheel to move one position and indicate the next lower digit. This process should continue until the counters of all orders reach zero. If further counts are recorded, the sign indicating device should be actuated to indicate a negative balance; and for succeeding counts, the counter wheels should be caused to move in the opposite direction with digits appearing in the sequence  $\cdots$  8, 9, 0, 1, 2  $\cdots$  and with counts being sent from one order to the next higher order as the corresponding counter wheel passes from 9 to 0. It is pos-

#### 16 Arithmetic Operations in Digital Computers

sible to design a counting mechanism which will perform a function such as this, but the requirements that the system be able to sense when the counters of all orders are at zero and that the counters be able to operate in either direction cause undesirable complexities in the mechanism.

If negative numbers were represented according to the pattern,

| +2 | 0002 |

|----|------|

| +1 | 0001 |

| 0  | 0000 |

| -1 | 9999 |

| -2 | 9998 |

it would be possible to avoid the zero sensing device and to use counter wheels which will function in one direction only. With the illustrated system for portraying negative numbers, it is not necessary to sense zeros to determine when the balance changes from positive to negative, because it is necessary only to detect when the thousands order counter moves from 0 to 9. Also in counting numbers beyond zero on the negative side, the counter wheels may function in exactly the same manner as for positive numbers. Another feature of this method of representing negative numbers is that the highest order counter wheel may be used to indicate the sign of the balance at the expense of the capacity of the counter. For example, a 9 indication in the highest order may be taken to indicate a negative balance with any other digit in this order indicating a positive balance. In this case, the capacity of the counter is from +8999 to -1000. If an 8 or a 9 in the highest order is used for a negative indication, the capacity is shifted to the range +7999 to -2000. The term used to describe this scheme for negative number representation is "10's complement," although the term is not to be interpreted to mean that each individual digit is a 10's complement. Actually, only the least significant nonzero digit is a 10's complement of the true digits; higher-order digits are 9's complements. For example, the 10's complement of 4680 is 5320. A more descriptive term would be "ten-thousand's complement," but this is clumsy.

Frequently it is desirable to employ a system for negative numbers similar to that just described in the counter itself but to convert the representation to that shown in the left-hand column when the result is recorded. For this purpose a slight but important modification is useful.

$$\begin{array}{ccc} +2 & & 0002 \\ +1 & & 0001 \\ 0 & & 0000 \text{ or } 9999 \\ -1 & & 9998 \\ -2 & & 9997 \end{array}$$

With this method of representation for negative numbers, the change to the commonly used system is made very conveniently by subtracting each individual digit from 9, and for this reason the representation is known as the 9's complement. The 9's complement may be generated when the counter goes from a positive to negative balance by using the signal obtained from the highest-order counter wheel as it passes from 0 to 9 to cause one additional count called "end-around borrow," to be registered in the units order. When counting in the positive direction from a negative balance, the counter will arrive at 9999 instead of 0000 for a zero indication. Then, when the next count is received, the signal which is obtained from the highest-order counter wheel may be used as an "end-around carry" to advance the units order counter from 0 to 1. From this point on, the counter will proceed in the usual manner and yield a true indication for positive balances. The balance sign indicator may be a separate device operated by the highest-order counter wheel, or, as before, the highest-order counter wheel itself may be used; but in this case the capacity for negative balances is reduced by 1, such as from +8999 to -999, when compared with the previous system.

The differences between true and complement notation become of increased importance when operations of addition and subtraction, other than by simple counting, are considered. On the other hand, for multiplication, the complement system frequently introduces more problems than it solves.

Similar ideas involving complement notation may be employed for the binary system or system of any other radix.

Nonintegral Quantities. There are two types of nonintegral quantities—those which may be represented as the ratio of two integers and are called rational (the integers themselves are rational), and those which cannot be represented as the ratio of two integers and are called irrational.

If it is desired to represent exactly a rational quantity, commonly called a fraction, it is usually done by recording the two integers involved, each with the same notation as used previously. The fact that the two integers are related is indicated on paper by writing one above the other with a line drawn between the two. It is conceivable that a computer could be designed whereby the position of the number in a storage unit is indicative of its function in a fraction, although the incorporation of a physical device to represent the line between the numbers appears to be somewhat superfluous. The advantages of a computer built along these lines would be realized only in certain special cases; and, in those cases where fractions must be dealt with in an exact manner, it has been found more practical to handle separately and independently in the computer

each of the two integers involved. The functional relationship between the two integers may be maintained through the programming of the sequence of arithmetic and other operations to be performed.

Usually it is not necessary, and sometimes it is not even desirable, that fractions be represented exactly. By extending the number system to include terms involving the negative powers of the radix, such as  $d_{-1}R^{-1}$ ,  $d_{-2}R^{-2}$ , etc., any fraction may be represented to any degree of accuracy. With this extension,

$$N = \cdots d_3 d_2 d_1 d_0 \cdot d_{-1} d_{-2} \cdots$$

The period or point between  $d_0$  and  $d_{-1}$  is used to signify the location of the units order, and the locations of all other orders are automatically specified. This point, called the decimal point in the decimal system, the binary point in a binary system, etc., is necessary when writing on paper because the digits corresponding to positive and negative powers of the radix are otherwise indistinguishable; but in a computer the orders may be assigned certain specific locations in the storage unit and are operated upon accordingly. Therefore, there is no need to provide an additional physical device in the computer for recording a counterpart of the dot (point) on a piece of paper. The assignment of the locations may change from problem to problem or even from step to step within a problem, but such changes are usually noted and recorded in the program. In general, it is possible to give an exact representation of a fraction by this scheme if the denominator of the fraction contains no prime factors which are not factors of the radix. An example is one eighth, which is 0.125 in the decimal system. The denominator of the fraction, one seventh, for example, contains a prime factor, seven, which is not a factor of ten. Therefore, one seventh cannot be represented exactly by this scheme, although by employing enough orders (0.1428571) ...) the difference between the indicated value and the exact value may be made as small as desired.

Some irrational numbers may be represented by integers with appropriate positional significance. For example, the integers 1, 2, and 3, if placed in the manner, 2½, represent the cube root of two. Much more exercise of the imagination is required to employ integers in the representation of irrational numbers derived from limits, trigonometric functions, and other sources. But, as in the case of fractions, an exact representation is not usually required anyway, and the customary procedure is to employ the same extension of the number system to terms involving negative powers of the radix in order to gain an approximate representation to any desired degree of accuracy.

Integral and Fractional Computers. Some computers are assumed to handle only integers and are therefore called integral computers, whereas in other computers the numbers are all assumed to have a magnitude less than unity, and these computers are called fractional. Although the difference between integral and fractional representation is of considerable importance when preparing a problem for solution by a computer, this difference is largely a figment of the imagination when considering the actual physical construction of the computer. But one physical difference worth mentioning lies in the disposition of the product after a multiplication. If a computer is built to handle numbers of a certain size, say four digits, the product of two of these numbers may contain eight significant digits. In an integral computer, if a number is to be added to the product, it should be added to the right-hand four digits, which are the ones of lesser significance. For the points to be lined up in a fractional machine, the addition should be to the left-hand, or most significant, digits. Sample computations of the kind AB + C for the two types of computers are shown below.

| $3023. \times 6104.$ |                   | .3023<br>× .6104     |           |

|----------------------|-------------------|----------------------|-----------|

| 18452392.<br>+ 4116. |                   | .18452392<br>+ .4116 | $AB \\ C$ |

| 18456508.            | $\overline{AB+C}$ | .59612392            | AB+C      |

| Integral             |                   | Fraction             | nal       |

Integral computers are most useful for problems which are essentially integral in nature; and many money calculations, for example, are of this type. With an integral computer, a quantity such as \$109.30 would be considered to be 10930, and the problem would be solved in cents instead of dollars and hundredths of dollars. At the conclusion of the problem, appropriate reconversions would be made.

The value of a fractional machine is realized for those problems where the data are not of an integral nature and where results of extreme accuracy either cannot or need not be obtained. Although the product of two four-significant-digit numbers may contain eight digits, it can be shown that only the four higher-order digits in the product are significant if the original factors were approximations and not exact representations. Actually, to say that a number has four significant digits implies that there is some doubt in the accuracy of the fourth digit; the extent of this doubt combined with certain fine points which may be included in the

definition of significance may indicate that the product has only three or as many as five significant digits, but in general the number of significant digits in the product is equal to the least number of significant digits in any one of its factors. In the above fractional example, the digits 2392 in the product AB are not significant and may be dropped. A subsequent addition should, therefore, be made to the left-hand four digits, as shown. If the factor C to be added were 0.004116, the last two digits may as well be dropped, because, even though they are significant in the factor C itself, they would not increase the number of significant digits in the result to any more than four when added to a product such as AB.

In an integral computer, therefore, the disposition of the product is such that subsequent additions are automatically made to the lowest orders, and special steps must be taken to handle any overflow into the higher orders. But in a fractional computer, the additions are automatically made to the highest-order digits of a product and the low-order digits are dropped unless special steps are taken to preserve them. In all but the most modest of computers it is possible to shift the digits in a number to lower or higher orders and thereby make additions of a number into any desired orders of a product, although the means for shifting vary greatly in convenience of operation and in required time in machines of different designs. Because of the ability to shift numbers, it is possible to perform fractional-type calculations on an integral machine and integral calculations on a fractional machine.

If the factors A and B in the fractional example had been 0.1342 and 0.1041, respectively, the product would be 0.01397022 with the four significant digits appearing in the second to the fifth positions to the right of the decimal point instead of the first to the fourth positions. For this and other reasons, frequent shifting is required for some problems; and, in general, the more shifting that is required for miscellaneous reasons, the less difference it makes whether the problem is solved on an integral or a fractional machine. Some computers are designed so that the orders into which a number is added must be specified for each addition. With computers of this type, either integral or fractional calculations may be performed with equal ease (or equal difficulty).

Floating-point Computers. A floating-point computer produces the effect of indicating the location of the point in a number, but the effect is accomplished through a means quite different from a physical indication between the digits. A number may be indicated by a series of digits multiplied by a power of the radix, where the point in the series of digits is understood to be always in the same place, such as to the left of the highest-order nonzero digit. The number, therefore, may be determined by the digits and the power, or exponent, of the radix. Some examples in the decimal system are listed below:

| Customary Notation |                           | Floating-point Notation |     |

|--------------------|---------------------------|-------------------------|-----|

| 8076000.           | $= 0.8076 \times 10^7$    | 8076                    | +07 |

| 80.76              | $= 0.8076 \times 10^2$    | 8076                    | +02 |

| 0.8076             | $= 0.8076 \times 10^{0}$  | 8076                    | +00 |

| 0.0008076          | $= 0.8076 \times 10^{-3}$ | 8076                    | -03 |

This floating-point type of notation is particularly useful for computations involving many multiplications and divisions where the magnitudes of the quantities involved are likely to vary widely and where only crude predictions can be made of the amount of variation. In multiplication, for example, the digits are multiplied in the usual manner, and the exponents are added. The main advantage of the system is derived from the ability to store very large or very small numbers by storing only the significant digits and the exponent; whereas, in a fixed-point machine, either integral or fractional, it is necessary to include all the zeros between the significant digits and the point or else keep track of the point through the programming of the problem.

In the examples shown above, the sign of the exponent is also of importance and must be recorded. The necessity of recording the sign can be avoided by assuming the point to be several orders to the left of the most significant digit. If it is fifty orders to the left, 0.8076, for example, would be thought of as  $0.00 \cdot \cdot \cdot 008076 \times 10^{50}$  and would be recorded as 807650 with the last two digits indicating the exponent of the multiplier. Of course, the range of exponents is halved by the dropping of the sign.

The floating-point system has an important disadvantage beyond the obvious fact that increased complexities are required to handle both significant digits and exponents in multiplication. Addition and subtraction, which are normally relatively simple operations, become much more difficult and time consuming than in fixed-point machines because of the necessity of shifting to match exponents before two numbers can be added together or subtracted one from the other. Also, overflows become more frequent. For example, the sum of two four-digit numbers can produce a five-digit number and require a shift to the right of one order and an increase by one in the exponent. Further, products and quotients must be tested for zeros to the left of the most significant digits and appropriate shifts executed when zeros are detected; otherwise there may be a gradual loss of significant digits as the computations proceed, which will be in addition to any losses caused by the mathematical nature of the problem.

With most large "general-purpose" fixed-point computers, it is possible

to perform computations in a floating-point manner by special techniques in the programming of the problems.

Mixed Radices. So far, it has been assumed that the radix of each term in a number is the same as the radix of all other terms. As might be expected, it is not necessary to impose a restriction such as this; and, in fact, in some fields of application, different radices are commonly used for different terms, especially for terms to the right of the point in comparison with the terms to the left of the point.

Although the decimal system is well adapted to the finger counting of integers, it is not so well adapted to the division of a quantity into parts. Anyone who has tried to cut an object into ten equal parts knows that it is not easy; whereas the cutting of the object into halves, then to fourths and eighths and so on, may be accomplished readily with reasonable accuracy. The cutting into thirds is also an awkward operation, but it is nevertheless a particularly frequent requirement. It is probably for reasons of this nature that in India the counting of rupees is done in the decimal system with the rupee divided into 16 annas, the anna divided into 4 pice, and the pice divided into 3 pie. The same reasons might have figured in the adoption by the English of 20 shillings to the pound, 12 pennies to the shilling, and 4 farthings to the penny, or in the adoption of the English system of weights and measures, which is badly scrambled with an assortment of radices. The linear measuring system, involving inches, feet, yards, rods, furlongs, and miles, is particularly confusing. The New York Stock Exchange employs the decimal system for dollars and a substantially binary system for parts of dollars in the representation of the price of stocks, even though the amount of money involved in any transaction is always indicated in dollars and cents. A possible justification for this practice is that a buyer and a seller can more readily establish a compromise price which is halfway between the bid and asked prices.

By using special codings for each digit in the conventional decimal system, another set of systems (including, notably, the biquinary system) may be derived; and some of these systems are often considered to be of the mixed radices type. However, it has been decided to omit these systems from the present discussion and to include them in the subject of decimal codes, because in almost every case the purpose of the coding is to make the decimal system more adaptable to computing machinery and because the mixed radices properties are usually incidental.

It is of interest to note that, in many cases where a mixed radices system has been established, it has been subsequently abandoned in favor of a pure decimal system. An example is surveying, where it is fre-

quently found desirable to replace inches with tenths of a foot. For mechanical machine work and other applications where small or accurate dimensions are involved, the practice of subdividing the inch into eighths, sixty-fourths, etc., has been largely replaced by the employment of the decimal system for fractional parts with the unit being the mil, or 0.001 of an inch. The division of pounds (weight) and gallons into tenths, instead of ounces and quarts, respectively, is frequent practice. The use of the decimal system for fractional parts in disregard of the established units is done for simplicity of notation and ease of computation and is evidence that any advantages which may be advanced in support of the mixed radices system cannot be very strong.

It is possible to design a special computer which will handle any one of the mixed radices systems fairly well, and in some simple applications a computer of this type is probably the best solution to the problem of performing computations once the system is established. An example is an adding machine for English or for Indian money, but a special adding machine would be useful only for the special application for which it was designed. A second solution to the problem is feasible when a more elaborate computer is employed, because then the computer itself can be used to execute conversions to pennies or annas, as the case may be, even though the machine operates with a number system of uniform radix. After the desired computations are completed, the computer can then reconvert the results into the desired units. Neither of these solutions is particularly satisfactory, however; and there is little doubt that the uniform radix systems are superior. As machine computations come into increased use, the reasons for abandoning the mixed radices systems become more compelling.

It should be pointed out that the mixed radices systems which have been mentioned employ the same decimal digits in every case instead of special digits as might be expected. For example, three thirty-seconds in a stock quotation is written  $\frac{3}{32}$ , and not 0.00011; also, thirteen shillings is written 13 where the 1 and the 3 together may be considered to be a new symbol, but it is more customary to view the digits with their usual decimal meaning. Details such as this, although of no fundamental importance, must be taken into consideration in the design of computing machinery.

Complex Numbers, Matrices, and Tensors. A complex number is customarily written as A + jB, where A and B are numbers according to previously described number systems, and j is the square root of minus one. As in the case of fractions, it is conceivable that a computer could be designed whereby the position of a number in a storage unit would indicate its function in a complex number and that addition, multiplication,

#### 24 Arithmetic Operations in Digital Computers

and other operations on complex numbers would be handled in the proper fashion automatically. For some classes of problems, particularly in communications and power engineering work, practically all quantities involved are most conveniently represented by complex numbers. For these problems a complex number machine has advantages, and at least one organization (Bell Telephone Laboratories) has constructed complex number machines. However, because a complex number computer would be inefficient when applied to other types of computations, and since the two parts, A and B, of a complex number are so easily handled separately with all individual arithmetic steps programmed, the usefulness of a machine designed especially for complex numbers appears to be of limited importance.

Similar remarks could be made with regard to madices, tensors, and other forms of mathematical symbols, but the over-all desirability of a machine built to handle such quantities automatically seems to be even less because of the great complications which would be necessary in the machine and because of the more limited application of the symbols.

Conclusions with Regard to Symbols. Although the advantages and disadvantages of the various systems of symbols can be pointed out, it does not appear possible to prove that any one system is better than all other systems.

It is a fact, however, that the systems employing the principle of position and a uniform radix are the only ones that have received wide acceptance; and if there is a system more adaptable to computers, it is probably one which has not yet been invented.

The important decision to be made is the choice of radix. Radix two is most attractive if machine simplicity is of prime importance, but the choice of radix ten is frequently dictated because of the desirability of using the computer in applications where the decimal system is already in general use. With large-scale high-speed computers, it is sometimes practical to employ the binary system internally in the computer and to use the computer itself to perform the necessary conversions between the decimal and binary systems in those cases where the use of the decimal system is required. The use of a binary computer with special conversion equipment to allow the use of the decimal system for data and solutions is also practical in some cases.

If the decimal system were not already so well established for general use, the choice might not fall on either the decimal or binary systems. In the choice of a radix, a compromise has to be made between the number of digits necessary to write a number and the number of different digits which it is necessary to employ. For the binary system only two different digits are required, but for any given number, over three times

as many digits are required for recording the value of the number, when compared with the decimal system. On the other end of the scale, to decrease the number of required digits by a factor of two, it is necessary to employ a radix of one hundred, which means that one hundred different digits would be required. Although radix ten appears to be a good compromise, radices eight and sixteen are also good compromises, and most of the advantages of the binary system can be realized with the octonary or sexadecimal systems.

The advantages of radix twelve are not derived from any particular adaptability of this radix to machine computations, and the advantage of radix three is slight at best and is found to be no advantage at all when the true nature of practically all currently available computer components is considered.

## Chapter 2

## BOOLEAN ALGEBRA APPLIED TO COMPUTER COMPONENTS

Boolean algebra derives its name from George Boole, who first introduced it in 1847 in a paper on the mathematical analysis of logic. The adaptability of this form of algebra to telephone and computer switching circuits appears to have been first pointed out by C. E. Shannon some ninety years later (1938) in the *Transactions* of the American Institute of Electrical Engineers. Since 1938 the interest in Boolean algebra and the extent of its use have grown rapidly with its growth closely paralleling the rapid development of complex switching networks as found in automatic telephone dialing systems and in large digital computers.

Boolean algebra is very different from ordinary algebra at first glance, and for this reason it may seem confusing or even a little ridiculous. Actually, it is an extremely simple algebra and, as will be shown, is of great value in the design of switching networks. However, one point should be understood from the start: it does not lead directly to the "best" circuit (usually the circuit with the least number of components, although sometimes other criteria are more important) in the same sense that, for example, calculus can be used to find minima in a function. What the algebra does provide is a convenient means of representing a switching circuit without drawing the circuit. Also, and probably more important, is the fact that it provides a means for quickly finding a multitude of different circuits that will perform any desired switching function. With a little practice, the circuit designer thereby has a powerful tool to aid him in finding a "good" circuit, even though it may not be the "best" one.

Basic Principles of Boolean Algebra. In Boolean algebra, there are only two different quantities or values which come into consideration, and these quantities are 0 and 1. Arithmetic operations in Boolean alge-

bra with "numbers" which can be only 0 or 1 bear little resemblance in meaning to the arithmetic operations in ordinary algebra, although in many instances the rules for performing the operations are the same. In particular, addition will be assigned the meaning of "or," and multiplication has the meaning of "and." The results obtained when "adding" and "multiplying" the various combinations of 0's and 1's are as follows:

$$0+0=0$$

$0 \times 0 = 0$

$0+1=1$   $0 \times 1 = 0$

$1+1=1$   $1 \times 1 = 1$

The first equation involving "addition" has the meaning, "0 or 0 is equal to 0." The second equation has the meaning "0 or 1 is equal to 1," because the "or" function, as indicated by the plus sign, serves to signify that the resultant quantity is 1 if either of the given quantities is 1. This interpretation of the "or" function includes the case where both of the given quantities are 1; therefore, "1 or 1 is equal to 1." Since there is no such quantity as 2 in Boolean algebra, the latter equation is, of necessity, different from anything found in ordinary algebra. A simple example of the Boolean algebra "or" function would be a fire-alarm device which may be actuated by signals from two different sources. The signal from each source may be represented by a 1, and the absence of a signal may be represented by a 0. The signal lines from the two sources should be combined so that the alarm will sound whenever a signal is received from either source. In other words, a signal is sent to the alarm when a signal is received from one source "or" the other source. Of course, if signals are received from both sources simultaneously, the alarm will sound in this case also, but not with twice the amplitude.

The equations involving "multiplication" have corresponding meanings, but with the word "and" substituted for "or." The "and" signifies that the resultant quantity is 1 only when both of the given quantities are 1. The last equation, which states that "1 and 1 is equal to 1," should not be confused with addition in ordinary algebra. An elementary example of an "and" function would be the firing of an explosive charge through the use of two signals where, in the interest of safety, it is required that both signals be present simultaneously in order to cause the charge to explode. The charge will explode only when a signal is received from one source "and" the other source also.

As in ordinary algebra, symbols may be used to represent "unknowns" or "variables," although the range of variation is limited to one or the other of the two discrete quantities, 0 and 1. The symbolic equation

C = A + B, for example, means that C is 1 if A "or" B is 1 (or if both are 1); otherwise, C is 0. Similarly, the equation C = AB means that C is 1 only if both A "and" B are 1; otherwise, C is 0.

From the above definitions, the following relationships may be obtained directly:

$$A + 0 = A$$

$$A + 1 = 1$$

$$A + A = A$$

$$A0 = 0$$

$$A1 = A$$

$$AA = A$$

The meaning of these equations may be readily understood by substituting for A each of the two possible values it may have.

Both the "or" and "and" functions are commutative and associative.

$$A + B = B + A$$

$$AB = BA$$

$$(A + B) + C = A + (B + C)$$

$$(AB)C = A(BC)$$

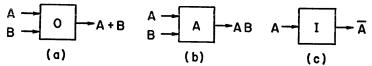

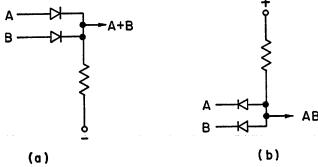

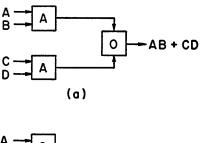

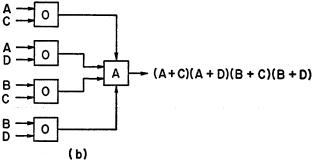

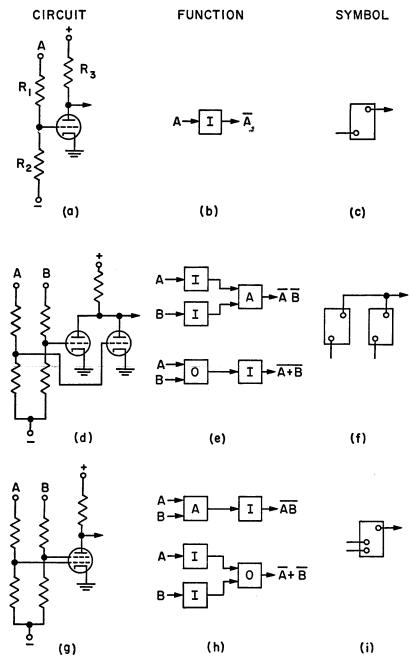

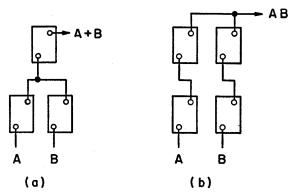

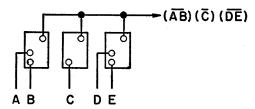

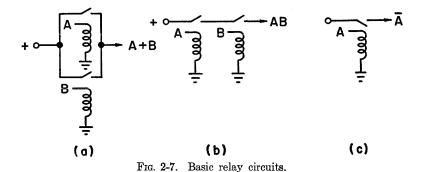

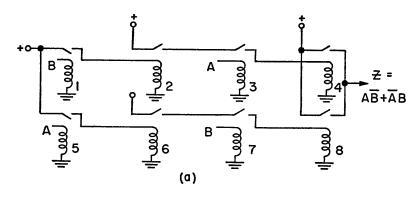

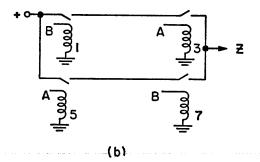

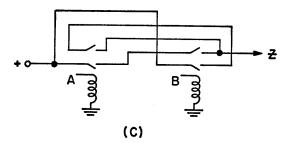

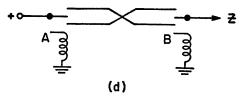

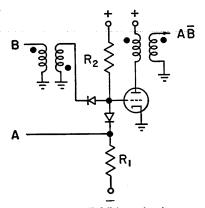

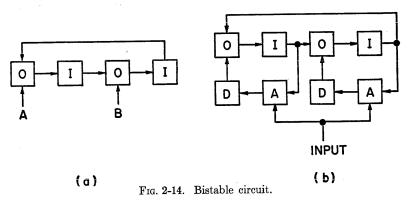

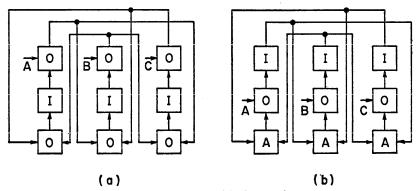

Also, each function is distributive with respect to the other.