#### **COMPUTER DESIGN AND ARCHITECTURE SERIES**

# Microprogrammable Computer Architectures Alan B. Salisbury

Microprogrammable

Computer

Architectures

#### **ELSEVIER COMPUTER SCIENCE LIBRARY**

#### Computer Design and Architecture Series

EDWARD J. McCLUSKEY, Editor

Salisbury Microprogrammable Computer Architectures

Svobodova Computer Performance Measurement and Evaluation

Methods: Analysis and Applications

Wakerly Error Detecting Codes, Self-Checking Circuits

and Applications (in prep.)

#### **ELSEVIER COMPUTER SCIENCE LIBRARY**

#### Computer Design and Architecture Series

EDWARD J. McCLUSKEY, Editor

Salisbury Microprogrammable Computer Architectures

Svobodova Computer Performance Measurement and Evaluation

Methods: Analysis and Applications

Wakerly Error Detecting Codes, Self-Checking Circuits

and Applications (in prep.)

# Microprogrammable Computer Architectures

Alan B. Salisbury

U.S. Army Electronics Command

### ELSEVIER NORTH-HOLLAND, INC. 52 Vanderbilt Avenue, New York, NY 10017

## ELSEVIER SCIENTIFIC PUBLISHING COMPANY 335 Jan Van Galenstraat, P.O. Box 211 Amsterdam, The Netherlands

© 1976 by Elsevier North-Holland, Inc.

Third Printing, 1977

#### Library of Congress Cataloging in Publication Data

```

Salisbury, Alan B

Microprogrammable computer architectures.

(Computer design and architecture series; 1)

(Elsevier computer science library)

Bibliography: p.

Includes index.

1. Electronic digital computers. 2. Microprogramming. I. Title.

QA76.5.$1995 001.6'4'04' 75-26337

ISBN 0-444-00175-1

ISBN 0-444-00176-1 pbk.

```

To Betty, Florence, and Kathy Yesterday, Today, and Tomorrow

#### **Contents**

| Prefac | e xi                                   |

|--------|----------------------------------------|

| Chapt  | er 1: Microprogramming in Perspective  |

| _      | Introduction 1                         |

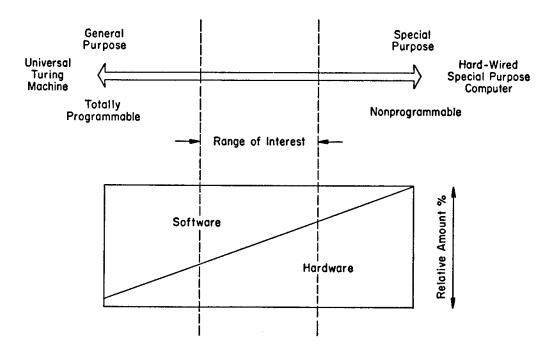

| 1.2    | Generality of Computers 1              |

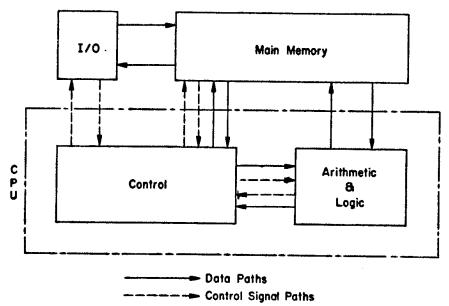

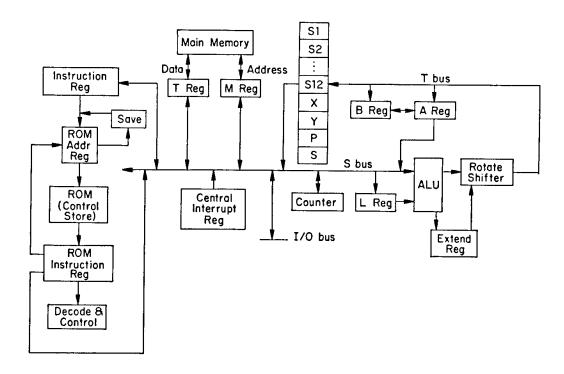

| 1.3    | The CPU and Computer Control           |

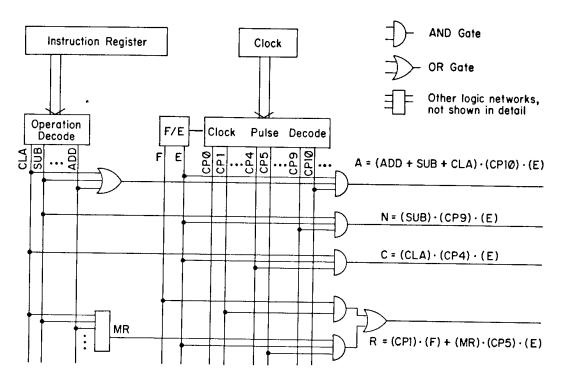

| 1.4    | Random Logic                           |

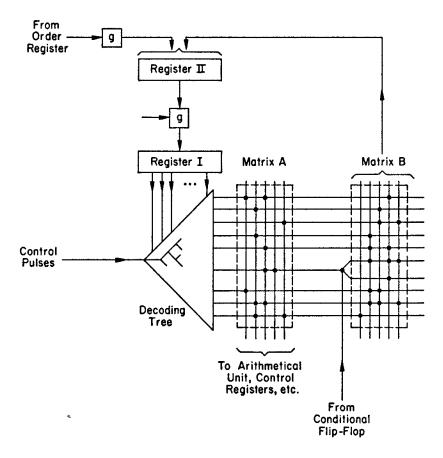

| 1.5    | The Microprogrammed Computer 5         |

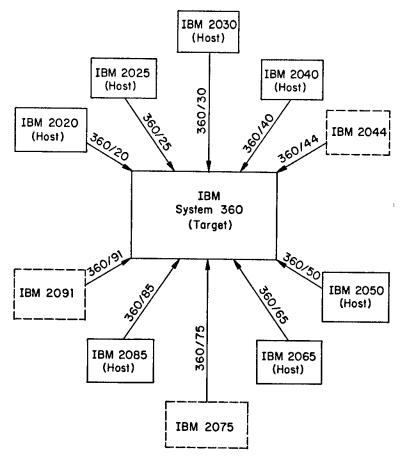

| 1.6    | Evolution through Emulation 8          |

| 1.7    |                                        |

| 1.7.   |                                        |

| 1.7.   | 2 Writable Control Store               |

| 1.7.   |                                        |

| 1.7.   | 4 Dynamic Microprogramming             |

|        | Firmware                               |

| 1.9    | Microprocessors and Microprogramming   |

| 1.10   | Architecture, Organization and Control |

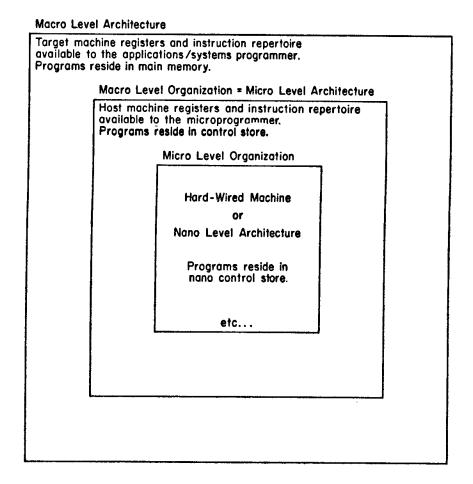

| 1.10   | 14 Levels of Control                   |

| 1.10   | Architecture and Organization Defined  |

| Chapt  | er 2: Architectural Facilities         |

| •      | in Microprogrammable Machines          |

| 2.1    | Introduction                           |

| 2.2    | Data Widths                            |

| 2.3    | Functional Processing Units            |

| 2.4    | Local Storage Facilities               |

| 2.5    | Control Storage Facilities             |

| 2.6    | Main Memory 29                         |

| 2.7    | Bus Structures                         |

| 2.8    | Interrupts                             |

| 2.9    | Input/Output 30                        |

| Chapter 3: Microinstructions and Control           |     |

|----------------------------------------------------|-----|

| 3.1 Introduction                                   | 32  |

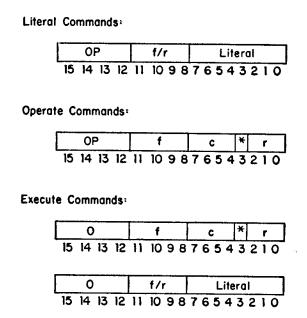

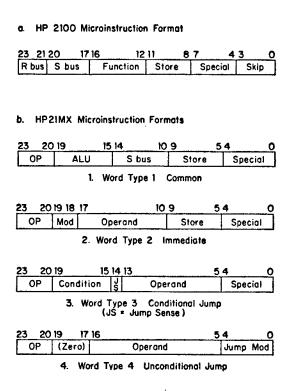

| 3.2 Microinstruction Formats                       | 32  |

| 3.2.1 Fixed/Variable Formats                       | 33  |

| 3.2.2 Degree of Encoding                           | 33  |

| 3.2.3 Number of Control Fields                     | 35  |

| 3.2.4 Microinstruction Timing                      | 34  |

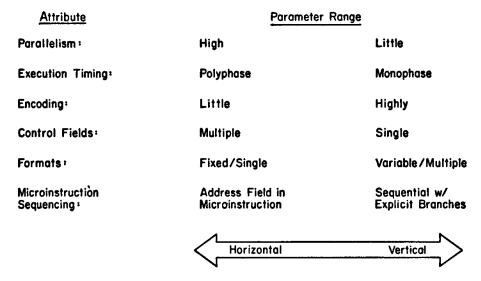

| 3.2.5 Horizontal/Vertical Microinstructions        | 36  |

| 3.3 Microinstruction Sequencing                    | 38  |

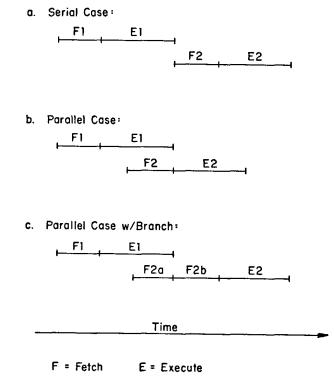

| 3.3.1 Fetch Timing                                 | 40  |

| 3.3.2 Next Address Selection                       | 11  |

| 3.4 Microinstruction Repertoire                    | 17  |

| 3.5 Microprogramming Languages                     | 15  |

| 3.6 Control Structures                             | 45  |

| 3.6.1 Distributed and Centralized Control          | 16  |

| 3.6.2 Residual Control                             | 17  |

| 3.6.3 Multilevel Control                           | 19  |

| 3.7 Summary                                        | ; 2 |

|                                                    | , , |

| Chapter 4: Microdata 3200 Architecture             |     |

| 4.0 Summary Description                            | :4  |

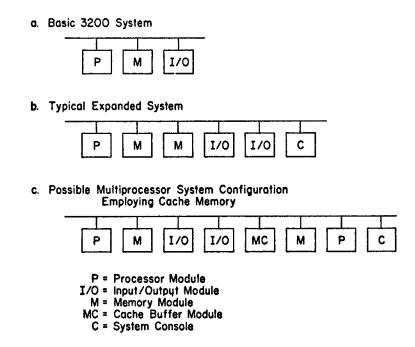

| 4.1 3200 System                                    |     |

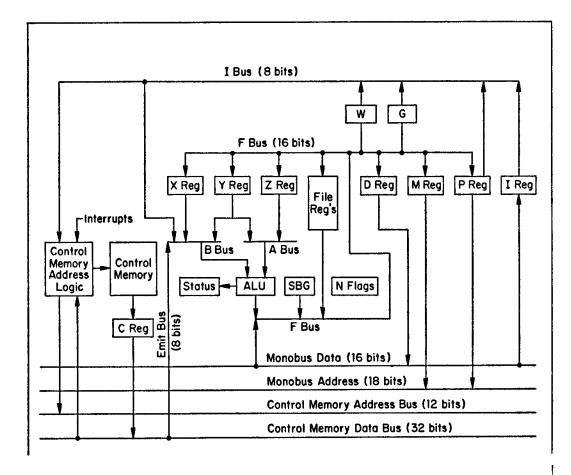

| 4.2 3200 Processor                                 | 5   |

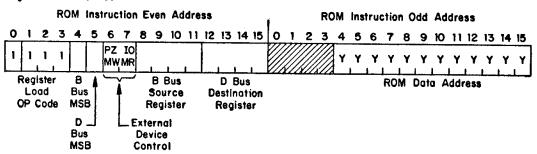

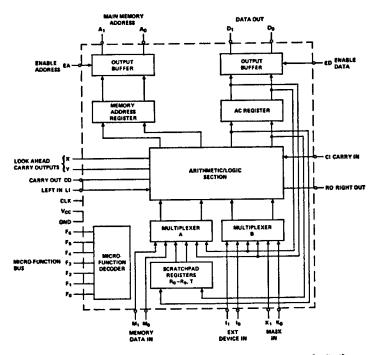

| 4.2.1 Processing Facilities                        | :5  |

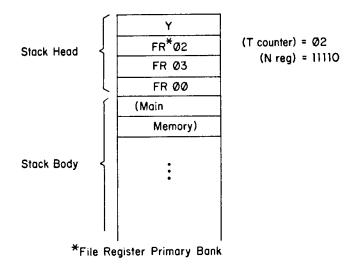

| 4.2.2 Local Store Facilities                       | :7  |

| 4.2.3 Control Store                                |     |

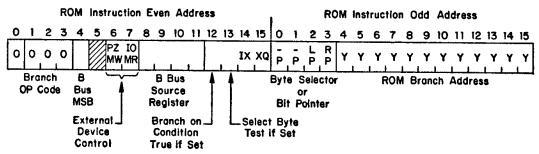

| 4.2.4 Microinstructions                            | 'n  |

| 4.3 Main Memory, Input/Output and the Monobus      | 4   |

| 4.4 Organizational Parameters                      | 5   |

| 4.5 Summary 6                                      | 5   |

|                                                    | J   |

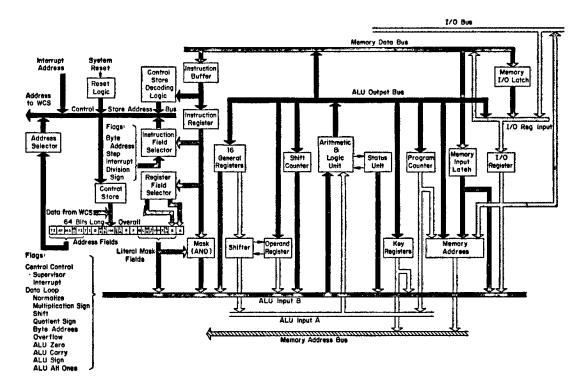

| Chapter 5: Interdata 8/32 Micro Level Architecture |     |

| 5.0 Summary Description 6                          | 7   |

| 5.1 Introduction 6                                 | 7   |

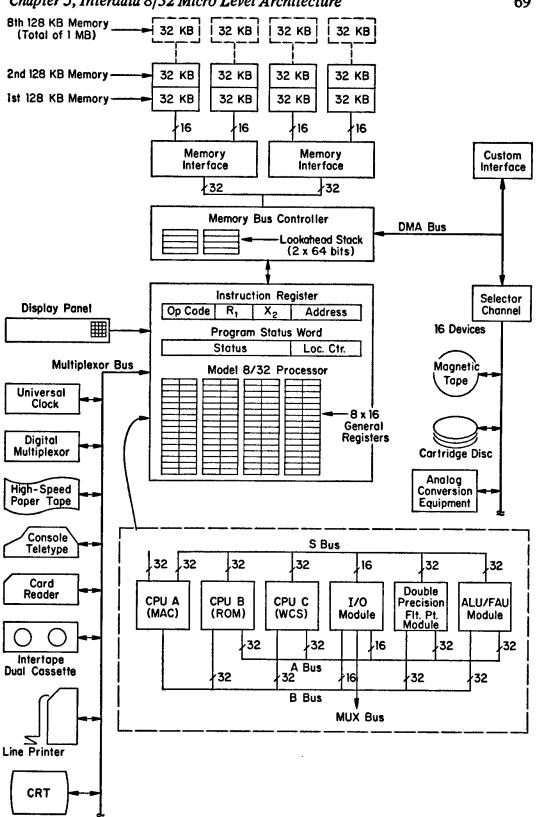

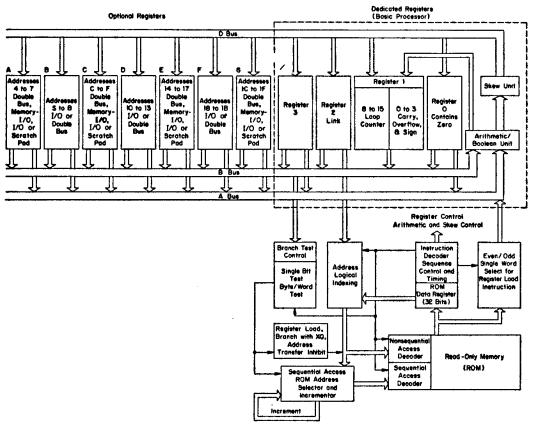

| 5.2 Model 8/32 Hardware                            | 8   |

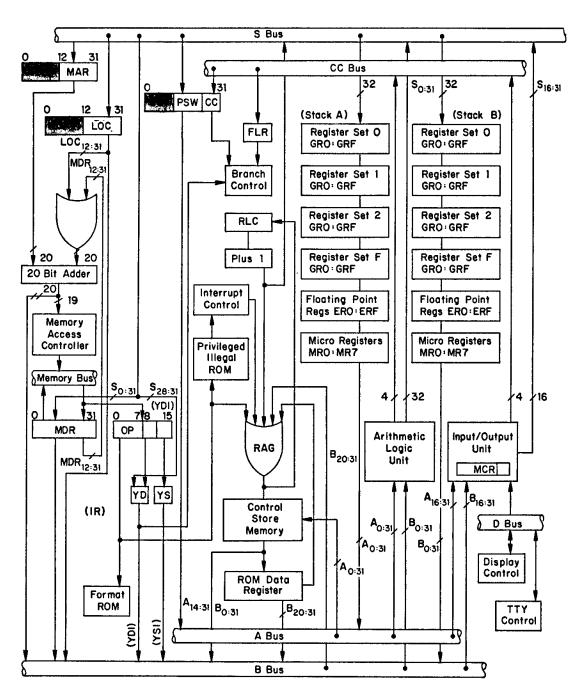

| 5.2.1 Processing Facilities 7                      |     |

| 5.2.2 Local Store 7                                | 1   |

| 5.2.3 Control Store 7                              | 9   |

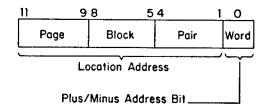

| 5.2.4 Main Memory 8                                |     |

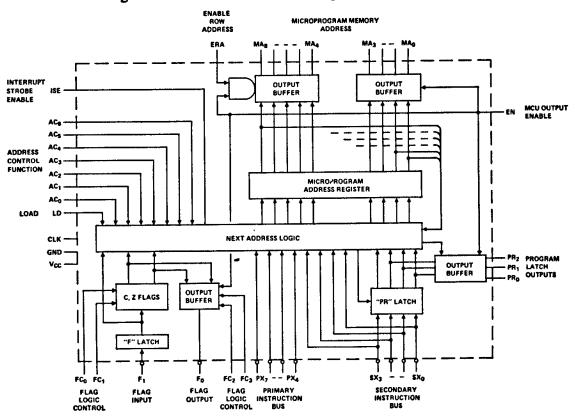

| 5.3 Model 8/32 Microinstructions and Control       | 2   |

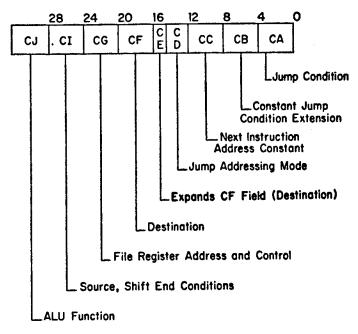

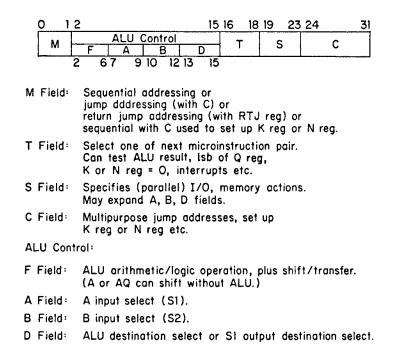

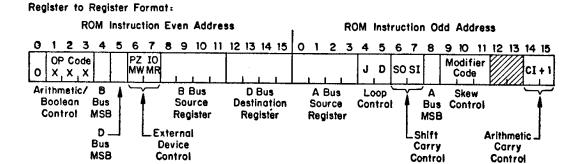

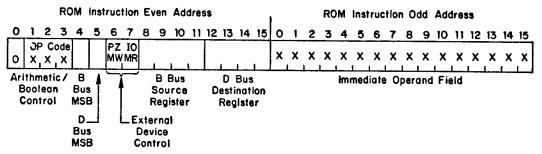

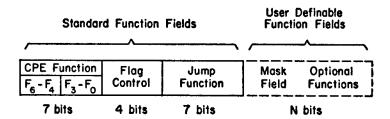

| 5.3.1 Microinstruction Fields                      | 2   |

| 5.3.2 Microinstruction Types                       |     |

| 5.3.3 Microinstruction Sequencing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.4 Interrupts 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.5 Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.6 Organization Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 6: Burroughs B1700 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.0 Summary Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.1 Introduction 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

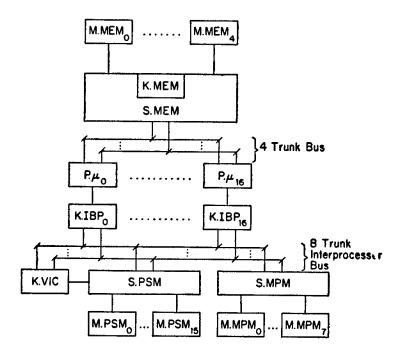

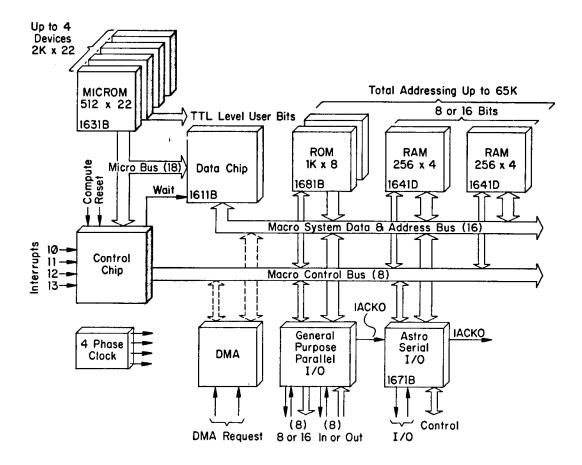

| 6.2 System Level Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.3 B1710 and B1726 Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

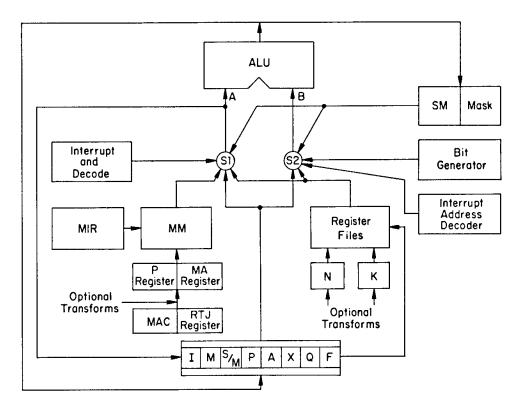

| 6.3.1 Processing Facilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.3.2 Local Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.3.3 Main Memory and Memory Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.3.4 Control Store100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

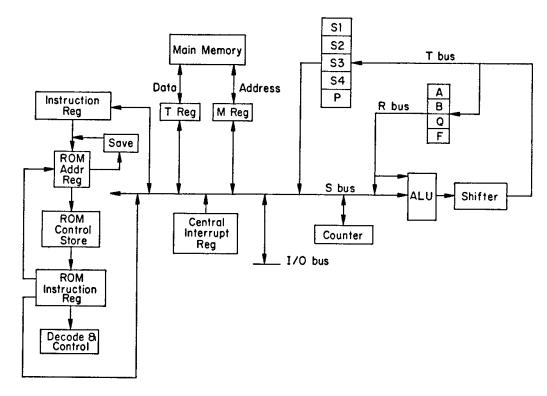

| 6.3.5 Microinstructions and Processor Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.4 Input/Output110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.5 Organizational Parameters110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.6 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

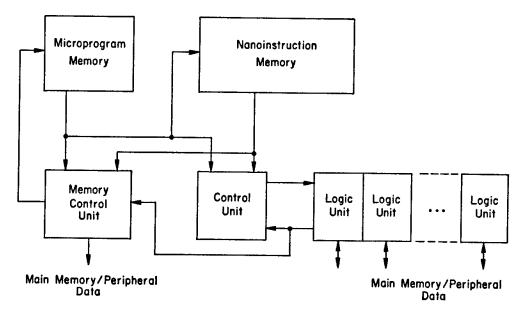

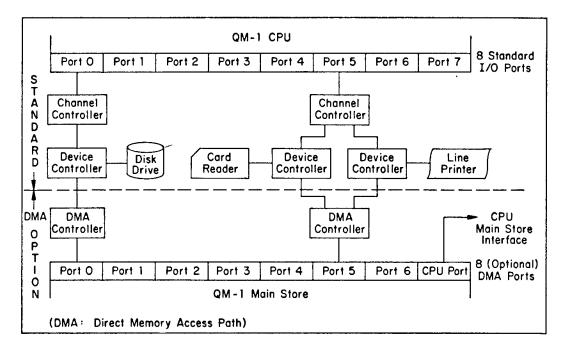

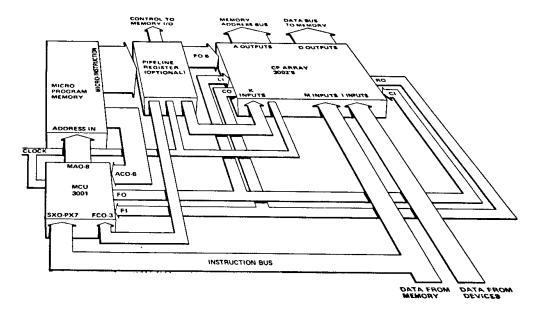

| Chapter 7: Nanodata QM-1 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.0 Summary Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

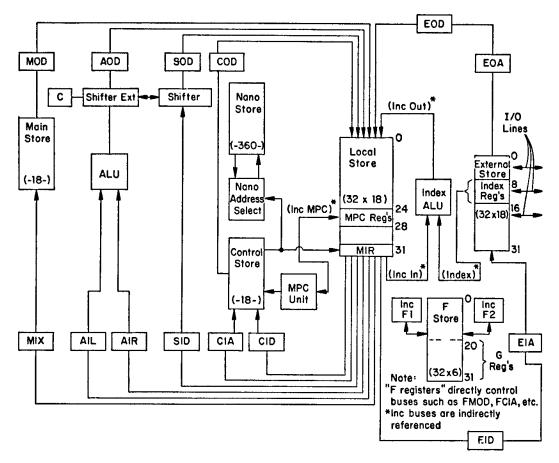

| 7.2 QM-1 CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

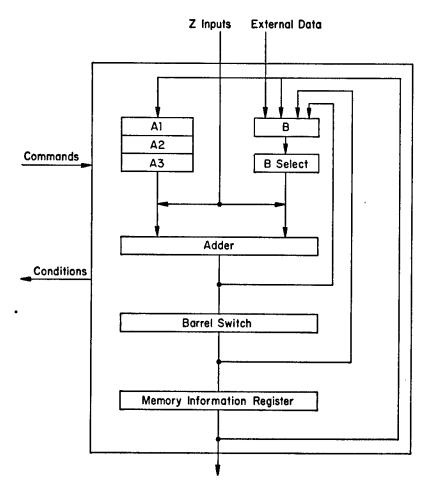

| 7.2.1 Processing Facilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.2.2 Local Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.2.3 External Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7.2.4 Control Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7.2.4 Control Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| The second of th |

| 7.2.7 Nano Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.3.2 Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.3.3 Nanoinstruction Sequencing and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |