# SIG MICRO NEWSLETTER

A Quarterly Publication of the Special Interest Group on Microprogramming

SEPTEMBER 1976

VOLUME 7

NUMBER 3

# **CONTENTS:**

NEW ORLEANS, LOUISIANA

acm Special Interest Group on Microprogramming

\* Technical Committee on Microprogramming

# Chairperson

Dr. Stanley Habib Polytechnic Institute of New York 333 Jay Street Brooklyn, New York 11201 212-643-3908

# Vice-Chairperson

Dr. Louise Jones

Information Systems Department

E.I. Dupont DeNemours & Co., Inc.

Wilmington, Delaware 19898

302-774-5389

# Secretary-Treasure

Ted G. Lewis

Department of Computer Science

Oregon State Unviersity

Corvallis, Oregon 97331

503-754-3273

## Newsletter Editor

Bruce D. Shriver Computer Science Department University of Southwestern Louisiana Box 4-43380 USL Lafayette, Louisiana 70504 318-233-3850 SIGMICRO Newsletter is an informal quaterly publication of the ACM Special Interest Group on Microprogramming whose scope of interest includes: Theory of Microprogramming; Applications of Microprogramming to Computer Control Systems; Use of Microprogramming by Computer Science Departments; Simulation based upon Microprogramming; Support Systems and other topics of interest to practitioners in the field of Microprogramming.

Membership in SIGMICRO is open to ACM members, associate members, and student members at a cost of \$4.00 per annum and non-ACM members, who are members of other professional societies whose major allegiance lies elsewhere, may also join at a cost of \$6.00 per annum. All members of SIGMICRO receive the Newsletter. A membership application including more details about joining SIGMICRO is included at the end of this publication.

Contributions to the SIGMICRO Newsletter should be sent to the Editor. Special camera-ready paper for typing manuscripts can be obtained from the Editor. All letters to the Editor will be considered for publication unless accompanied by a request to the contrary. Except for editorial items, all sources of material appearing in the SIGMICRO Newsletter will be clearly identified. Items attributed to individuals will ordinarily be interpreted as personal rather than organizational opinions.

SEPTEMBER 27-29, 1976 **NEW ORLEANS, LOUISIANA**

Sponsored by acm Special Interest Group on Microprogramming ( IEEE COMPUTER SOCIETY Technical Committee on Microprogramming

Institute of Electrical and Electronics Engineers, Inc.

Copyright 1976 by

The Association for Computing Machinery 1133 Avenue of the Americas New York, New York 10036

And

The Institute of Electrical and Electronics Engineers, Inc. 345 East 47th Street New York, New York 10017

IEEE Catalog No. 76CH1148-6C

Copies available from:

ACM 1133 Avenue of the Americas New York, New York 10036

IEEE Computer Society 5855 Naples Plaza, Suite 301 Long Beach, California 90803

IEEE Service Center 445 Hoes Lane Piscataway, New Jersey 08854

Manufactured in the U.S.A.

# TABLE OF CONTENTS

|                                                                                                                          | PAGE      |

|--------------------------------------------------------------------------------------------------------------------------|-----------|

| A Bit Slice Architecture for Microprogrammable Machines by Michael Andrews                                               | 5         |

| Certification of Microprogrammum, s by an Algebraic Method by A. Blikle and S. Budkowski                                 | 9         |

| Microgrammed Implementation of a Scheduler by Rahul Chattergy                                                            | 15        |

| An Insight into PDP-11 Emulation by J. C. Demco and T. A. Marsland                                                       | 20        |

| Design Problems In Emulating the MIX Computer on the Microdata 1600 by T. Don Dennis and O. G. Johnson                   | 27        |

| Extensibility - a New Approach for Designing Machine Independent Microprogramming Languages by David J. DeWitt           | 33        |

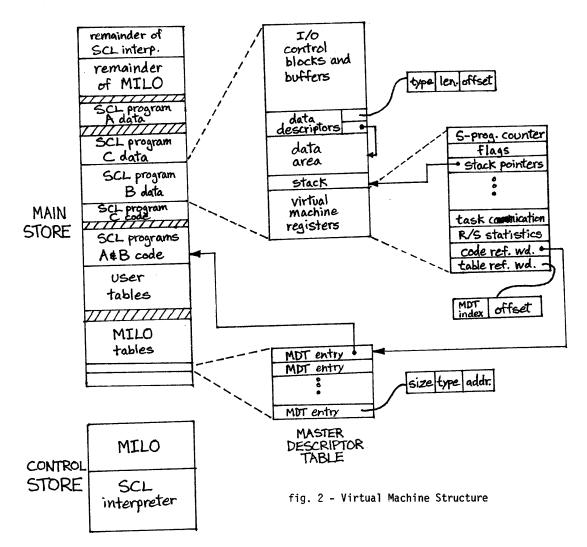

| Realizing a Virtual Machine<br>by B. Forbes, T. Weidner, R. Yoder, and T. Pitchford                                      | 42        |

| The FORTRAN Project - A Multifaceted Approach to Software -<br>Firmware High Level Language Support<br>by Gideon Frieder |           |

| Automated Proofs of Microprogram Correctness<br>by W. H. Joyner, W. C. Carter, and G. B. Leeman                          | .47<br>51 |

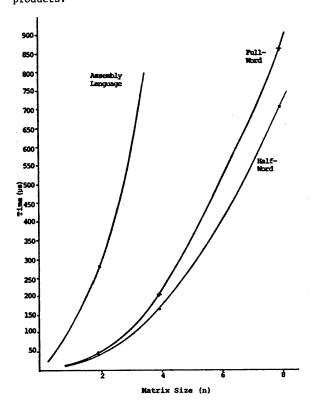

| A Microprogrammed Machine Architecture for Efficient Matrix Multiplication                                               | 31        |

| by Robert Nowlin and Donald Gustafson                                                                                    | 56        |

# A BIT SLICE ARCHITECTURE FOR MICROPROGRAMMABLE MACHINES\*

# Michael Andrews Department of Electrical Engineering, Colorado State University Ft. Collins, Colorado 80523

The use of a bit slice architecture offers an attractive alternative to the design of microprogrammable computing architectures. By bit slice we mean typically a LSI chip containing either a 2 bit, 4 bit where n is very small. This paper describes these particular architectures to design in horizontal microprogramming. Hardware design implementations for both fixed point and floating point arithmetic algorithms are proposed. Experiences with these numerical hardware are discussed, along with problems encountered.

### 1. INTRODUCTION

Until recently, computing hardware for original design has been based mainly upon LSI (large scale integration) chips which, at a minimum, were 8 bits wide. Generally, configurations have been implemented with 16 bit chips. Now it is possible to design architectures with chips that are very short word width, of the order 2 or 4 bits. This is made possible with the introduction of several industrial chips, [1-4], and others. These short width LSI packages offer some versatility in the design and control of computing architectures for variable word length scenarios. Typically such applications are found in the process control industry, numerical control of milling machines, etc., and other on-line control applications. In this paper we propose some architectural designs using these bit-slice chips. It is found that an additional vehicle for horizontal microprogramming is now possible.

The paper begins with a description of the bitslice architecture of the INTEL series. The next section discusses a hardware design using a modified INTEL 3000 in a floating point processor. This section is followed by a discussion of the microprogramming sequencing techniques employed in the 3000 series. The paper ends with a discussion of the use of the 3000 as a vehicle for demonstrating microprogramming techniques. At this point, however, we mention that a major modification to the INTEL 3002 CPE chip, for our studies, was made in order to employ horizontal microprogramming. In particular, rather than use commercial functions, our functions were devised on the basis of the availability of control gate connections. These connections are hypothesized to permit elementary microoperations. In this way, it is possible to demonstrate the actual timing requirements internal to any CPU given this control gate accessibility. The discussion to follow focuses briefly upon the 3000 series and our modifications to the CPU chip.

### BIT SLICE ARCHITECTURES

This section provides a brief overview of a bit

\*This work was supported by the AFAL under grant F 33615-75-C-1138

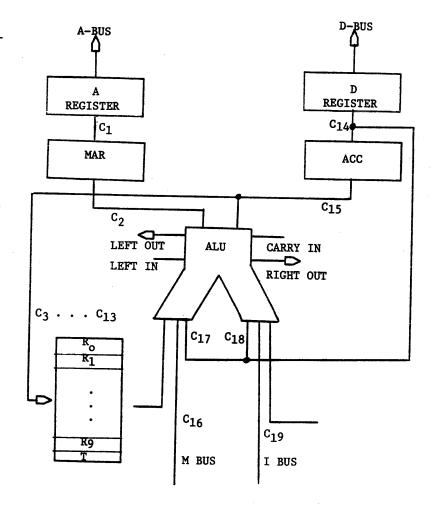

slice architecture, the Intel 3000 Series. The 3000 series is configured around two LSI, a 3002 central processing element (CPE), and a 3001 microprogram control unit (MCU)[5]. With ancillary hardware to enhance sophisticated implementations, they include a carry look-ahead generator, pipeline latches, clocks. The CPE chip is a basic ALU which does primitive boolean functions, excluding left-shifts. This absence of a left-shift indeed penalizes some macroinstruction programming as will be shown later. The ALU has two input sources via 2 buses, an M bus and an I bus. However, the I bus is maskable with another bus, the K bus, which allows for byte manipulation and bit masking. The ALU outputs to two destinations, a memory address register and an AC (accumulator) register. However, it has been found in practice that the AC does not perform as a typical accumulator. Rather, an eleven cell scratch pad serves more suitably as the traditional accumulators. The CPE also contains the necessary function bus decoder logic to control the ALU and register transfers. Lastly, carry-in and-out, left-in, and right-out signal lines are available. When cascaded to form an 8 bit or 16 bit macro-ALU, the configuration is controlled by cascades of the chip, which serves as the microprogram sequencer. No address incrementer is available. Thus, all sequencing is via jump addresses [6].

### 3. FIXED POINT BIT SLICE ARCHITECTURE

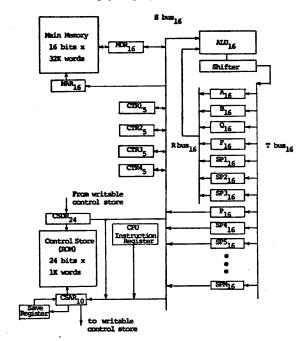

Implementation of a fixed point binary machine, 16 bits wide has been accomplished with eight 2 bit CPE's similar to the Intel 3000 Series. See fig. 1.

Modifications were made to the commercially available CPE chip in order to provide for a horizontal micro control structure [7,8]. This is accomplished by assuming that the individual control gates internal to the CPE chip are available to the microprogrammer as a field in the microinstruction. There are 5 fields in each microinstruction: the control field for the control gates,  $C_1$  through  $C_{19}$ , a K field of 16 bits, a function field of 4 bits labeled  $F_6$  through  $F_3$ , an address field and a T-field (for branch testing). Each microinstruction word was 42 bits wide not including the next address field which, of course, depends on the total microprogram content for any machine. The structure in the microprogram control was assumed as a horizontal machine. Thus simultaneous register activity could result in the CPE chips. However, because the chip accumulator did not serve as such in the traditional sense, and because the scratch-pad registers were used as accumulators, this particular configuration placed some penalty upon the microprogram size. As a result, for most of the fixed point add and subtract, and all of the fixed point multiply and divide routines, extra microinstructions were required to maintain an accumulating partial product or partial remainder. For a typical nonrestoring division routine by successive additions 30 microinstructions were required. This assumed that the AC held the divisor, and the scratch-pad registers contained the partial remainder, divident, and shift-right bit counters. Although the 3000 series microprogram format assumes an R group concatenated with an F group for the on-chip function decoder, our configuration assumed the function decoder was simply 4 bits wide instead of 7. Scratch-pad control gates C3 through C13, both enabled the input and output gates of each scratch-pad cell respectively. This then required that any scratch-pad cell use become both a source and destination for micro operations when called. Without this modification it would have been necessary to add at least 10 more bits to the microinstruction field length for additional control gate signals.

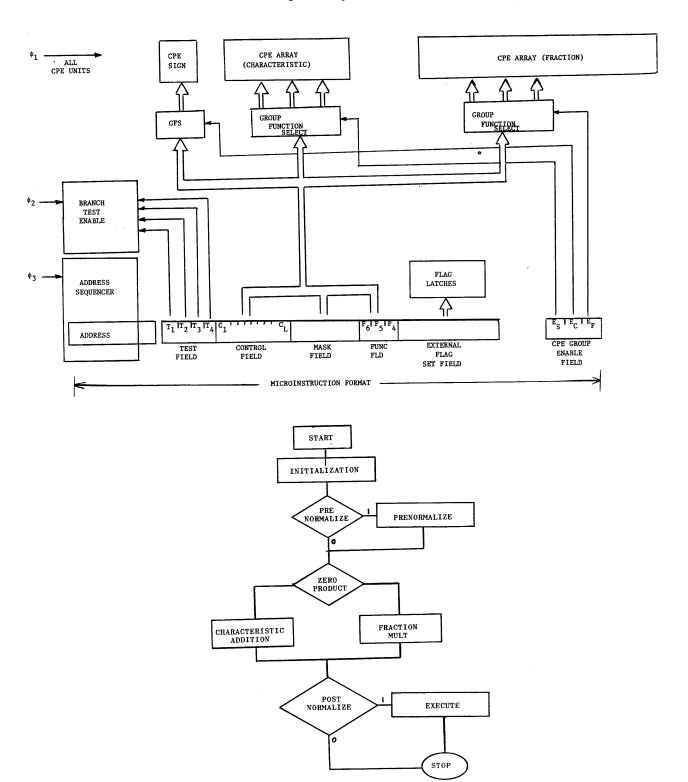

# FLOATING POINT BIT-SLICE ARCHITECTURE

Floating point architecture again assumes an Intel 3000 CPE chip modified for horizontal microprogramming. However, it was desirable to speed up floating point manipulations. Thus, additional hardware was included to perform some parallel processing. The word format for this machine assumed a sign magnitude notation number system with 16 binary bits for the fraction and 8 binary bits for the characteristic (with offset or bias). For this configuration, then, 8 CPE chips were cascaded for the fraction portion of the algorithm and 4 CPE chips were cascaded for the characteristic portion. Horizontal control, however, allowed for arithmetic functions in both the characteristic and fraction ALUs. This form of parallel processing decreased the execution time of typical floating point manipulations, at the cost of a wider microinstruction width. The hardware for the floating point design is shown in Fig. 2.

Here, like the fixed point design, a T-field was included in the microinstruction word for microinstruction branching during the second phase of our 3 phase clock. In addition, some divide overflow and characteristic underflow indicators were available and reserved in the flag set field of the microinstruction. It was found desirable to include also a CPE group enable field to allow inhibiting of either the fraction of characteristic ALU when so desired. The additional gating required to implement our floating point processor is also shown. These include some miscellaneous control gates which are enabled by the test bits from the CPE chips.

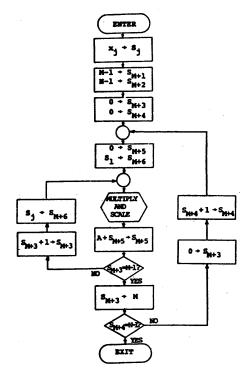

The timing sequence for the processor and microprogram control includes a 3-phase clock with phase 3 designated for fetch cycle, phase 1 for the execute cycle, and phase 2 for branch decision. This timing reflects solely the microprogram control. Additional clocking is required, of course, for microprogram and main-memory cycles, not shown. A typical parallel processing algorithm is shown for the floating point multiply routine of Fig. 3.

Here, initialization and characteristic alignment precede the prenormalization check as with most floating point algorithms. A decision for zero product is made next. This is followed by the parallel processing of the characteristic addition and the fraction multiply. Because an ALU exists for both operations, these arithmetic sequences can be performed in parallel. Upon completion of the sequence, a postnormalization decision is made and the procedure terminates after the normalization is required. A similar flow chart follows for the floating point divide. For our floating point multiply routine and the floating point architecture shown, it was possible to microprogram the floating point multiply in approximately 60 microinstructions. Again, the scratch-pad served as the accumulating partial product and partial remainder while the chip accumulator held the divisor or multiplier during processing.

### 5. CONCLUSIONS

A hardwired floating-point processor designed about a bit-slice architecture has been proposed. Microprogram implementations for multiplication have been described. It is seen that the for certain commercially available LSI architecture, modifications to traditional functional element roles were necessary. In particular, the AC in the Intel 3001 CPE functions more like a latch than an accumulating register. Also, further modifications to the CPE control gate structure were introduced to emphasize a horizontal microprogrammable machine. Use of cascaded chips allowed for independent fraction and characteristic ALU blocks. Horizontal control, then, permitted simultaneous parallel activity, though, at the expense of increased microinstruction word width. One unresolved question is the relative comparison of our architecture to others, namely, the Intel 3002 unmodified cascaded configuration.

### ACKNOWLEDGMENT

The author wishes to acknowledge the contributions of Robert Emberty, Daniel Eggerding and Greg Lipinsky who analyzed processor designs with floating point microprograms.

### REFERENCES

- INTEL Series 3000 Microprogramming Manual, Intel Corporation, Santa Clara, Calif., 1975, 1-10.

- [2] AM 2901, AM 2909 Technical Data Manual, Advanced Microdevices, Incorporated, Calif., 1975.

- [3] J. Mick, "AM 2900 Bipolar Microprocessor Family," Electronics, 8th Annual Workshop on Microprogramming, Chicago, Ill., Sept. 1975, 56-63.

- [4] J. Rattner, J. Cornet, and M. E. Hoff, "Bipolar LSI Computing Elements Usher in New Era of Digital Design," <u>Electronics</u>, vol. 47, no. 18, Sept. 5, 1974.

- [5] Central Processor Design Using the INTEL Series 3000 Computing Elements, <u>Application</u> <u>Note AP-16</u>, Intel Corp., Santa Clara, Calif., 1975.

- [6] J. F. Wakerly, C. P. Hollander, and D. Davies, "Placement of Microinstructions in a Two-Dimensional Address Space," 8th Annual Workshop on Microprogramming, Chicago, Illinois, Sept. 1975, 46-51.

- [7] G. Reyling, "Considerations in Choosing a Microprogrammable Bit Sliced Architecture,"

<u>Computer</u>, vol. 7, no. 7, July 1974, 26-29.

[8] T. Lee, "LSI Microprocessors and Micropro-

- [8] I. Lee, "LSI Microprocessors and Microprograms for User Oriented Machines," MICRO-7 Annual Workshop on Microprogramming, Palo Alto, Calif., Oct. 1974, S-1 through S-9.

Fig. 1 - Modified Processor Chip

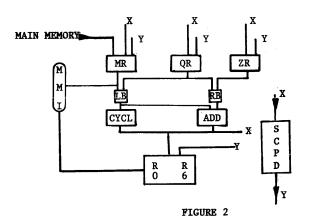

Fig. 2 Floating Point Processor

Fig. 3 Floating Point Mult

### CERTIFICATION OF MICROPROGRAMS BY AN ALGEBRAIC METHOD

A. Blikle\*

Computation Center

Polish Academy of Sciences

00-901 Warsaw, Poland

S. Budkowski\*\*

Dept. of Computer Science

Warsaw Technical University

00-665 Warsaw, Poland

This algebraic method provides a mathematical framework for proving input-output properties (such as partial and total correctness) of iterative programs. Technically it uses a calculus of binary relations extended with fixed-point equations. The method has been tested on several microprograms of a computer's arithmetical unit. One example of such a microprogram and its correctness proof is discussed in the paper.

### 1. INTRODUCTION

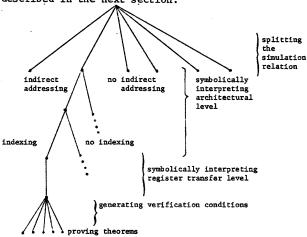

In the current literature of the subject one can distinguish two different trends of attacking the problem of the mathematical certification of microprograms. In one approach ([2],[9],[11],[12]) the analyzed microprogram and its expected meaning are described by two abstract machines one of which is defined on the hardware level and the other on the level of architecture. The correctness proofs consist of showing that one of these machines simulates the other in the sense defined by R. Milner [15]. In the other approach the expected meaning of a microprogram is described by more mathematical (or less operational) terms either by verification conditions [16], which involves Floyd's method, or by regular expressions [10] which involves the algebra of events together with the related fixed-point equations. In the latter two cases one refers to some standard mathematical methods of software-program verification.

This paper presents another software-program verification method ([3],[4],[5],[8],[14]) applied to microprograms [6]. The general idea of this method is the following: Given a program  $\mathbb I$  its meaning is assumed to be a binary input-output relation  $\mathbb R$  (I-O relation) which describes the mapping of the initial values of the vector of variables into the terminal values of this vector.

To establish R explicitly we split the program  $\Pi$  into a finite number of modules  $\Pi_1,\ldots,\Pi_n$  (e.g. assignment statements and tests) which must be simple enough for their I-O relations  $R_1,\ldots,R_n$  to be obvious. Since the program  $\Pi$  is a combination of  $\Pi_1,\ldots,\Pi_n$  the relation R must be a combination of  $R_1,\ldots,R_n$ :

$$R = \Psi(R_1, \dots, R_n) \tag{1.1}$$

The function  $\Psi$  is defined in the algebra of relations (Sec.2) and describes the control structure of  $\mathbb T$ . To find the function  $\Psi$  we use an algebraic method which consists of writing and solving a set of fixed-point equations in our algebra. Once  $\Psi$  has been found, we use (1.1) in the further analysis of  $\mathbb T$ . This analysis is carried out in the algebra of relations and permits proofs of partial as well as total correctness of programs.

The general method above was applied by the authors to several arithmetical microprograms of a floating-point arithmetical unit designed at the Warsaw Technical University. This application has raised a problem which is usually neglected in the consideration of software programs. Namely, the arithmetical microprograms involve computer arithmetics which is fairly different from the usual (Peano's) arithmetics. E.g. in the computer arithmetics the law of the distributivity of multiplication by  $2^{-1}$  (arithmetical shift right) does not hold. The lack of this property makes the calculations which appear in the verification of the microprogram practically impossible. To solve this problem we consider two programs  $\Pi_1$  and  $\Pi_2$ , where  $\Pi_1$  is the "real" microprogram and  $\Pi_2$  is an abstract program resulting from  $\bar{\mathbb{I}}_1$  by the replacement of the machine operations by the corresponding arithmetical ones. We verify the program  $\Pi_2$  and then we show that  $\Pi_2$  simulates  $\Pi_1$  in the following sense: Let F1 and F2 denote the I-O functions of  $\Pi_1$  and  $\Pi_2$  respectively, let  $D_1$  and  $D_2$  denote the input domains of  $\Pi_1$  and  $\Pi_2$  (i.e. the domains of  $F_1$  and  $F_2$ ) and let  $D_1 \subseteq D_2$ . There exists a function

Part of this work was done when the author was visiting the Dept. of Comp. Sci., University of Waterloo. This part was supported by the National Research Council of Canada under Grant A-1617.

<sup>\*\*</sup>Part of this work was done when the author was visiting the Department of Computer Science, Uni-varsity of Maryland. This part was partially supported under grant NSF DCR75-05505.

$T:D_2\to D_1$  such that T(d)=d for all  $d\in D_1$  and  $F_1(\overline{T}(d))=T(F_2(d))$  for all  $d\in D_2$ . Now all the I-O properties of  $\mathbb{I}_2$  can easily be "translated" into the I-O properties of  $\mathbb{I}_1$ . This concept of simulation coincides, of course, with the algebraic simulation of R. Milner [15] which apparently makes our approach similar to that of A. Birman, B. Leeman and W. Carter. As a matter of fact, however, our program verification is not restricted to the proof of simulation but also provides the proof of the total correctness of  $\mathbb{I}_2$ .

The organization of the paper is the following: First we describe the general Blikle-Mazurkiewicz method which is slightly modified here in regard to the form of fixed-point equations (this permits dealing with programs which have more than one output and proving their local properties see [7]). Next we show a detailed example of the verification of a software program II3 which performs the Booth fixed-point multiplication algorithm and is a simplified version of an abstract program N2 which in turn simulates the real microprogram  $\Pi_1$ . We describe the modifications required in  $\mathbb{T}_3$  to get  $\mathbb{T}_2$  and the modifications of  $\mathbb{T}_2$ which result  $\Pi_1$ . Referring to the analysis of  $\Pi_3$ we describe briefly the analysis of  $\Pi_2$  and show the function of simulation T between  $\bar{\mathbb{I}}_1$  and  $\mathbb{I}_2$ .

# 2. THE ALGEBRA OF BINARY RELATIONS

Let D be an arbitrary nonempty set called the  $\underline{domain}$  and interpreted as the set of all possible states of the vector of variables in a program. By Rel(D) we denote the set of all  $\underline{binary}$  relations in D, i.e. Rel(D) =  $\{R \mid R \subseteq D \times D\}$ . For any a,b in D and R in Rel(D) we shall write aRb for (a,b)  $\in$  R. By  $\phi$  we shall denote the  $\underline{empty}$  relation, and by I the  $\underline{identity}$  relation, i.e.  $I = \{(a,a) \mid a \in D\}$ .

Basic operations in the set Rel(D), which we shall use in the sequel, are defined below. Let  $R_1, R_2 \in \text{Rel}(D)$ .

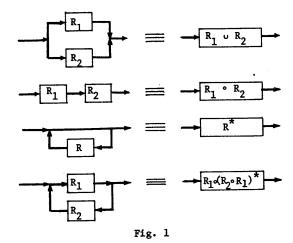

Interpretation. The operations  $\upsilon$ , °, \* are used in the descriptions of the I-O relations of programs; precisely speaking they are used to describe explicitly the function  $\Psi$  in (1.1). Fig.1 shows the interpretation of the operations defined in this section. Each box in fig.1 represents a module of a flowchart of a microprogram with input-output relation  $R_1$ . These modules may be viewed either as elementary (with I-O relations described by assignment statements or tests) or as submicroprograms which consist of a number of elementary boxes. This permits the structuring of analyzed microprograms.

Below we list the most important properties of these operations. Here and in the sequel we shall omit the symbol "o" of composition and write  $R_1R_j$  instead of  $R_1 \circ R_j$ .

1)

$$R_1(R_2R_3) = (R_1R_2)R_3$$

- associativity

2)

$$R_1(R_2 \cup R_3) = R_1R_2 \cup R_1R_3$$

- finite distributivity  $(R_2 \cup R_3)R_1 = R_2R_1 \cup R_3R_1$

3)

$$R_0(\overset{\circ}{U}R_1) = \overset{\circ}{U}R_0R_1$$

- infinite distributivity  $(\overset{\circ}{U}R_1)R_0 = \overset{\circ}{U}R_1R_0$   $\overset{\circ}{I}$

5)

$$R\phi = \phi R = \phi$$

- the zero property of  $\phi$

6)

$$R* = I \cup R^{+}$$

$R^{+} = RR* = R*R$

7)

$$R_1(R_2R_1)*R_2 = (R_1R_2)*R_1R_2$$

To deal with concrete programs (and microprograms) and to carry out their analysis we shall need an explicit notation to specify the I-O relations. Since we are going to deal only with deterministic programs, we can restrict ourselves to the case of partial functions and use the notation introduced by A. Mazurkiewicz [8]. A relation  $R \subseteq D \times D$  is a partial function if for any  $d_1 \in D$  such that  $d_1Rd_2$ .

Let  $f:D \to D$  be an arbitrary partial function and let  $p:D \to \{true, false\}$  be an arbitrary predicate such that if p(d) = true then f(d) is defined. We denote by

$$[p(x) | x := f(x)] =$$

(2.1)

=  $\{(d_1, d_2) | p(d_1) = \text{true & } d_2 = f(d_1)\}$

Of course, [p(x) | x := f(x)] is a partial function whose domain is  $\{d | d \in D \& p(d) = true\}$ . For the sake of simplicity we shall also write [x := f(x)] for [true | x := f(x)] and [p(x)] for [p(x) | x := x]. Of course [p(x)][x := f(x)] = [p(x) | x := f(x)]. In the sequel we shall use the following equivalences which can be proved easily from (2.1):

1)

$$[p(x)|x := f(x)][q(x)|x := g(x)] =$$

=  $[p(x) & q(f(x))|x := g(f(x))]$  (2.2)

2)

$$[p(x)|x := f(x)] \cup [q(x)|x := f(x)] =$$

=  $[p(x) \vee q(x)|x := f(x)]$

### 3. THE MATHEMATICAL MODELS OF PROGRAMS

In order to define in a rigorous way the concept of the I-O relation, we need here a rigorous concept of a program. To this effect, we shall use the notion of an algorithm introduced by A. Mazur-kiewicz [8].

By an <u>algorithm</u> we shall mean any system  $A = (D, V, \alpha_1, T)$  where

- D is an arbitrary nonempty set called the  $\frac{\text{domain}}{\text{Sec. 2}}$ ,

- V =  $\{\alpha_1, \dots, \alpha_n\}$  is a finite nonempty set of elements called <u>labels</u> of the algorithm,

- $\alpha_1$  is a distinguished element of V called the  $\underline{\text{initial label}}$  of the algorithm,

- $\begin{array}{ll} -\overline{J} &= \{\alpha_{1},R_{1j},\alpha_{j}\} \mid R_{1j} \in \text{Rel}(D); \ i,j \leq n \} \ \text{is a} \\ \text{set of p = n}^{2} \ \text{triples called } \underline{\text{instructions}}. \ \text{Usually} \\ \text{many of the } R_{i,j} &= \phi \ \text{which describes the fact that} \\ \text{there is no direct trespassing between } \alpha_{1} \ \text{and } \alpha_{j} \\ \text{in the program. Given an instruction, the corresponding } \alpha_{i}, R_{i,j} \ \text{and } \alpha_{j} \ \text{are called the} \ \underline{\text{entrance}} \\ \underline{\text{label}}, \ \text{the } \underline{\text{action}} \ \text{and the} \ \underline{\text{exit label}}. \ \overline{\text{The } \alpha_{i}}'s \\ \text{are interpreted as the control states} \ \text{and the} \\ R_{i,j}'s \ \text{define the meaning of "boxes"}. \end{array}$

We are going to apply our theory to deterministic programs only. Nevertheless, the theory itself will be developed in the general nondeterministic case which makes its presentation much simpler.

Consider an arbitrary algorithm  $A = (D, V, \alpha_1, J)$  where  $V = \{\alpha_1, \dots, \alpha_n\}$ . For any  $\alpha_1, \alpha_j \in V$ , by an  $(\alpha_1, \alpha_j) - \underline{\operatorname{run}}$  we shall mean any sequence of instructions of J.

$$(\alpha_{i_1}^{R_1,R_1,\alpha_{j_1}}); \dots; (\alpha_{i_k}^{R_k,R_k,\alpha_{j_k}})$$

(3.1)

such that  $\alpha_{i_1} = \alpha_i$ ;  $\alpha_{j_k} = \alpha_j$  and  $\alpha_{j_p} = \alpha_i$  for p+1  $p \le k-1$ . Of course, an  $(\alpha_i, \alpha_j)$ -run is simply a path in the graph of A. The corresponding sequence of actions  $(R_1, \ldots, R_k)$  will be called an  $(\alpha_i, \alpha_j)$ -symbolic execution (s. execution). Let  $\text{Exec}(\alpha_i, \alpha_j)$  denote the set of all the  $(\alpha_i, \alpha_j)$ -s. executions in A. The  $(\alpha_i, \alpha_j)$ -resulting relation is defined as follows:

This is of course the I-O relation of A under the assumption that  $\alpha_1$  is the input label and  $\alpha_4$  is the output label. Indeed  $d_1 \text{Res}(\alpha_1,\alpha_j) d_2$  iff there exists an  $(\alpha_1,\alpha_j)$ -s. execution  $(R_1,\ldots,R_k)$  such that  $d_1 R_1 \circ \ldots \circ R_k d_2$ . Observe that in any  $(\alpha_1,\alpha_j)$ -run the control of the algorithm may pass through  $\alpha_1$  and  $\alpha_j$  many times.

By the definition of A the label  $\alpha_1$  is assumed to be initial and therefore we shall be interested mostly in the relations  $R(\alpha_1,\alpha_j)$  for  $j=1,\ldots,n$ . Moreover, among these n relations we shall select usually some number of  $k \le n$  relation that correspond to the actual outputs of the program. The particular one-output case corresponds to k=1, but in some applications we may want to consider programs with more than one output (e.g. the successful termination, the overflow and the underflow).

Now suppose we are considering an algorithm A where  $\alpha_\Pi$  has been chosen to be the terminal label and suppose that we have proved

$$Res(\alpha_1, \alpha_n) = [p(x) | x := f(x)].$$

(3.3)

By the definition of Res( $\alpha_1,\alpha_j$ ) this implies the following about A:

- for every initial d ∈ D the algorithm terminates (stops) if and only if p(d) is satisfied,

- 2) for every initial  $d \in D$  if the algorithm terminates, then the terminal value of x is f(d).

Of course 2) is a partial-correctness property of A and 1) defines exactly the domain of termination. Consequently, (3.3) is the strongest total-correctness property of A, since p(x) is not only sufficient but is also a necessary condition of termination (for the concepts of partial and total correctness see [13]).

# FIXED-POINT EQUATIONS AND PROGRAMS

Dealing with concrete programs we shall attempt to express their resulting relations  $\operatorname{Res}(\alpha_1,\alpha_j)$  in terms of the actions of instructions  $R_{1j}$  and the operations defined in Sec.2. The definition (3.2) does indicate how to do it (see  $\operatorname{Res}(\alpha_2,\alpha_3)$  in Sec.5), but finding  $\operatorname{Res}(\alpha_1,\alpha_j)$  this way may be difficult even for a program of middle complexity. Below we present a method of fixed-point equations which permits to find all  $\operatorname{Res}(\alpha_1,\alpha_j)$  for programs of any complexity. These equations differ from the ones used previously (see [7] for detailed explanations).

Let  $A = (D, V, \alpha_1, J)$  be an arbitrary algorithm with  $V = (\alpha_1, \ldots, \alpha_n)$ . By the <u>canonical set of equation</u> (CSE) of A we mean the set:

$$x_1 = x_1 R_{11} \cup \dots \cup x_n R_{n1} \cup R_{11} \dots$$

(4.1)

$$X_n = X_1 R_n \cup \dots \cup X_n R_{nn} \cup R_{1n}$$

where every  $R_{ij}$  is, of course, the action of the instruction  $(\alpha_1,R_{ij},\alpha_j)$  in J . The unknowns  $X_i$  of

(4.1) range, of course, over the set Rel(D) of relations. Any vector  $(P_1, \ldots, P_n)$  of relations which satisfies (4.1) is called a solution of this set. In the general case  $(4.\overline{1})$  has more than one solution. The solution  $(P_1, \ldots, P_n)$  is said to be the <u>least solution</u> if for any other solution  $(Q_1,\ldots,Q_n)$  we have  $P_i\subseteq Q_i$  for i = 1,...,n. It is a well-known fact that the least solution, if any, is unique. In our case we can prove the following:

Theorem 1. For any algorithm A the vector of relations (Res $(\alpha_1,\alpha_1),\ldots,$ Res $(\alpha_1,\alpha_n)$ ) is the least solution of the corresponding CSE.

The proof is described in [7]. Here we shall show an effective method of solving (4.1). The method consists in the application of two variable-elimination transformations:

- 1. Substitution: the substitution of  $X_1R_{1i}$  u ... u  $X_nR_{n1}$  u  $R_{1i}$  for an arbitrary occurrence of  $X_i$  on the right side of (4.1).

- Iteration: the replacement of the equation  $\overline{X_i = X_1 R_{1i}} \cup \dots \cup X_i R_{ii} \cup \dots \cup X_n R_{ni} \cup R_{1i}$ by the equation

$$X_{i} = (X_{1}R_{1i} \cup ... \cup X_{i-1}R_{i-1i} \cup$$

$$\cup X_{i+1}R_{i+1} \cup \ldots \cup X_{n}R_{ni} \cup R_{1i})R_{1i}^*$$

Each of these transformations is applicable to any set of equations like (4.1) and yields another set of equations of the same form. As can be proved (see [5] for the references) the new set of equations has exactly the same least solution as the former. To solve a given CSE we keep applying our transformations as long as there are some unknowns (variables) on the right side.

# AN EXAMPLE OF A SOFTWARE-PROGRAM VERIFICATION

The method described in this paper has been tested on several arithmetical microprograms of a floating-point arithmetical unit designed at the Warsaw Technical University. One of these microprograms, call it N1, performed Booth's algorithm of the fixed-point multiplication of mantissas. We analyzed  $\Pi_1$  by introducing and verifying an abstract program  $\Pi_2$  and by proving that  $\Pi_2$  simulates  $\Pi_1$ (see Sec. 1 and 6). Here we shall investigate a simplified version of  $\Pi_2$ , call it  $\Pi_3$ , which differs from  $\Pi_2$  in neglecting overflows. In spite of this simplification the example still provides an adequate flavor of the method. In Sec.6 we show how to extend these calculations to deal with the real cases of  $\Pi_2$  and  $\Pi_1$ .

In our program we shall deal with numbers represented in the 2's complement code: The numbers from the interval (-1,1) are represented as:

$$\beta = -\beta_0 + \sum_{i=1}^{n} \beta_i * 2^{-i}$$

(5.1)

where  $\beta_i \in \{0,1\}$  for i = 0,...,n and  $n \ge 1$  is fixed. We shall also use the equation

$$\beta = \sum_{i=0}^{n} (\beta_{i+1} - \beta_i) * 2^{-i}$$

(5.2)

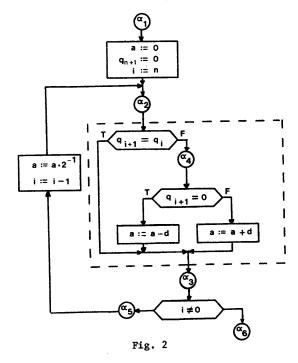

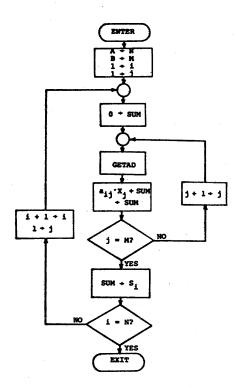

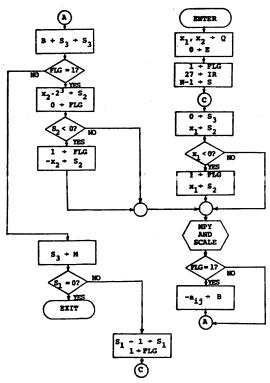

which follows from (5.1) under the condition that  $\beta_{n+1} = 0$ . The flowchart of our program  $II_3$  is given in fig. 2.

This program operates on the following variables:

- 1) the real variable a which ranges over an arbitrary interval of real numbers (this is actually the assumption which neglects the overflow),

- 2) the real variable d which ranges over (-1,1),

- 3) the integer variable i which ranges over {0,..n},

- 4) the 0's and 1's array q[0:n+1].

We shall prove that the program performs the multiplication  $(-q_0 + \sum_{i=1}^{n} q_i * 2^{-j})*d$  and stores the result

In the calculations we shall use an extension of the notation introduced in Sec.2. Namely, for any vector of variables  $(x_1,...,x_n)$ , the function  $[(x_1,...,x_n) := (f_1(x_1,...,x_n),...,f_n(x_1,...,x_n))]$  will be written as

$$\begin{bmatrix} x_1 := f_1(x_1, \dots, x_n) \\ \dots \\ x_n := f_n(x_1, \dots, x_n) \end{bmatrix}.$$

(5.3)

Of course all the assignment statements in (5.3) are understood to be performed simultaneously. We assume also to omit in (5.3) all the assignment statements of the form  $x_i := x_i$ .

We shall prove the following about our program:

Res

$$(\alpha_1, \alpha_6)$$

=

$$\begin{bmatrix} a := (-q_0 + \sum_{j=1}^{n} q_j * 2^{-j}) * d \\ i := 0 \\ q_{n+1} := 0 \end{bmatrix}$$

(5.4)

According to the definition of  $\operatorname{Res}(\alpha_1,\alpha_j)$  (see also the remarks by the end of Sec.2) this implies that our program terminates everywhere in its domain and that it performs the multiplication of the number whose representation is stored in q[0:n] by the number which is stored in d.

To simplify the calculations let's consider first a module of fig.2 between the control states  $\alpha_2$  and  $\alpha_3$ . For this simple program we can find the Res( $\alpha_2, \alpha_3$ ) directly from the definition (3.2). Namely (using (2.2)):

$$\operatorname{Res}(\alpha_{2}, \alpha_{3}) = [q_{i+1} = q_{i}] \cup \\ \cup [q_{i+1} \neq q_{i}]([q_{i+1} = 0 | a := a-d] \cup \\ \cup [q_{i+1} = 1 | a := a+d]) = \\ = [q_{i+1} = q_{i} | a := a+(q_{i+1} - q_{i})*d] \cup \\ \cup [q_{i+1} = 0 \& q_{i} = 1 | a := a+(q_{i+1} - q_{i})*d] \cup \\ \cup [q_{i+1} = 1 \& q_{i} = 0 | a := a+(q_{i+1} - q_{i})*d] = \\ = [a := a+(q_{i+1} - q_{i})*d].$$

In the next step we establish the CSE of the program of fig.2:

$$X_1 = \phi$$

$X_2 = X_5 R_{52} \cup R_{12}$

$X_3 = X_2 Res(\alpha_2, \alpha_3)$

$X_5 = X_3 R_{35}$

$X_6 = X_6 R_{36}$

ere

$$R_{52} = \begin{bmatrix} a := a \times 2^{-1} \\ i := i - 1 \end{bmatrix} ; R_{12} = \begin{bmatrix} a := 0 \\ q_{n+1} := 0 \\ i := n \end{bmatrix}$$

$$R_{35} = [i \neq 0]; R_{36} = [i = 0]$$

Solving this set with respect to  $\mathbf{X}_{6}$  we get  $X_6 = R_{12} (Res(\alpha_2, \alpha_3) R_{35} R_{52})^* Res(\alpha_2, \alpha_3) R_{36}.$

By Theorem 1 we have, of course,  $X_6 = \text{Res}(\alpha_1, \alpha_6)$ .

$$S_{k} = \begin{bmatrix} a := \sum_{i=1}^{k} (q_{n+1-k+1} - q_{n-k+1}) *2^{-i} *d \\ i := n-k \\ q_{n+1} := 0 \end{bmatrix}$$

and for all  $k \ge 1$  denote

$$P_k = R_{12} (Res(\alpha_2, \alpha_3) R_{35} R_{52})^k$$

.

We can prove by induction (see [7] for details) that for all  $1 \le k \le n$  we have  $P_k = S_k$ . We can prove also [7] that the loop in our program must be performed exactly n times, which formally means (c.f.

$$\operatorname{Res}(\alpha_1, \alpha_6) = \operatorname{S}_{n} \operatorname{Res}(\alpha_2, \alpha_3)[1=0]$$

By straightforward calculations we get now

$$\operatorname{Res}(\alpha_{1},\alpha_{6}) = \begin{bmatrix} a := \sum_{i=0}^{n} (q_{i+1} - q_{i}) * 2^{-i}) * d \\ i := 0 \\ q_{n+1} := 0 \end{bmatrix}$$

which by (5.2) gives us the required result (5.4). This terminates the proof of the total correctness of the program II3.

It can be observed [7] that using our method one can also prove some local properties of the program, as for example the estimation of the current value of a at the label  $\alpha_2$  and  $\alpha_3$ .

# AN EXAMPLE OF A MICROPROGRAM VERIFICATION

Let us consider now the program  $\Pi_2$  which differs from II3 in the following:

- 1) d ranges over numbers representable by (5.1) for n = 23

- a ranges over numbers representable by (5.1) for n = 47 (generally speaking  $n \ge 47$ )

- to the assignments a := 0;  $q_{n+1} := 0$ ; i := n for n = 23 the assignment z := 0 is added

- 4) the assignments a := a±d are replaced respectively by:

where

$$\begin{cases} -1; & x < -1 \\ 0; & -1 \le x < 1 \\ 1; & 1 \le x \end{cases}$$

5) the assignment  $a := a*2^{-1}$  is replaced by:

$$\frac{1f}{z} = 0$$

$\frac{1}{z} = a*2^{-1}$   $\frac{1}{2} = a*2^{-1} + a_0$

This means that  $R_{52}$  is equal now

$$R_{52} = [z=0|a := a*2^{-1}; i := i-1; z := 0] \cup [z=1|a := a*2^{-1} + a_0; i := i-1; z := 0]$$

Following the same way as in Sec.5 - just with more calculations - we can prove the following:

$$\operatorname{Res}_{2}(\alpha_{1}, \alpha_{6}) = \begin{bmatrix} a := q*d - 2*0vf(q*d) \\ i := 0 \\ q_{24} := 0 \\ z := 0vf(q*d) \end{bmatrix}$$

(6.1)

where  $\operatorname{Res}_2(\alpha_1,\alpha_6)$  is the appropriate I-O relation in

$$\Pi_2$$

,  $q = \sum_{i=0}^{23} (q_{i+1} - q_i) * 2^{-1}$  and a is the 48-bit rep-

resentation of the required result (double precision) .

Now consider the original microprogram  $\Pi_1$  for which the length of a is assumed to be 24-bit only (single precision). Every occurrence of  $a*2^{-1}$  in  $\Pi_2$  must now be replaced by a  $92^{-1}$  since the computer multiplication 9 by  $2^{-1}$  (arithmetical shift right of the content of the register storing a) is no longer the usual one. Observe that in general

$$a = 2^{-1} = a*2^{-1} - a_n*2^{-(n+1)}$$

and only for  $I_2$  (and  $I_3$ ) a  $0 \ 2^{-1} = a * 2^{-1}$ .

Of course, we could use this equation with n=23 to replace every occurrence of a 0  $2^{-1}$  in  $\Pi_1$  by its right side and to get an equivalent program  $\Pi_1$  with only usual arithmetical operations. The analysis of such a program, however, would be very cumbersome. It is much easier to observe that  $\Pi_2$  simulates  $\Pi_1$  and to verify  $\Pi_2$ . Let us describe briefly what the simulation of  $\Pi_1$  by  $\Pi_2$  looks like.

In the original case of our analysis we proceed, of course from  $\Pi_1$  to  $\Pi_2$ . First we establish the algorithm  $A_1 = (D_1, V, \alpha_1, J_1)$  which corresponds to  $\Pi_1$ . The domain  $D_1$  is the set of all the vectors of the form  $(a,d,q_0,\dots,q_{24},i,z)$  where a and d range over these numbers in  $\langle -1,1\rangle$  which can be represented by (5.1) with n=23, and the other variables have the ranges as described earlier. Next we establish the algorithm  $A_2 = (D_2,V,\alpha_1,J_2)$  which corresponds to  $\Pi_2$  and which differs from  $A_1$  only in  $D_2$  and  $J_2$ . The set  $D_2$  results from  $D_1$  by letting a range over all numbers in  $\langle -1,1\rangle$ . The set  $J_2$  results from  $J_1$  by replacing every instruction  $(\alpha_1,R_{1j},\alpha_j)$  by the instruction  $(\alpha_1,R_{1j},\alpha_j)$ , where  $R_{1j}$  results from  $R_{1j}$  - informally speaking by replacing all a 0 2 by  $a*2^{-1}$ . Now, for any number  $\beta \in \langle -1,1\rangle$  whose standard 2's complement representation is

$$\beta = -\beta_0 + \sum_{i=1}^{\infty} \beta_i * 2^{-i}$$

1et

$$t(\beta) = -\beta_0 + \sum_{i=1}^{24} \beta_i * 2^{-i}$$

.

The function t( $\beta$ ) effectuates, of course, the "truncation" necessary in order to store  $\beta$  in a register of 24 bits. The simulation relation between  $\Pi_1$  and  $\Pi_2$  is the function  $T:D_2 \to D_1$  defined as follows:

$$T(a,d,q_0,...,q_{24},i,z) =$$

=  $(t(a),d,q_0,...,q_{24},i,z)$

Of course  $D_1 \subseteq D_2$  and T(v) = v for all  $v \in D_1$ . Now it is an easy task to check the following [see 7]:

$$TR_{ij} = \hat{R}_{ij}T$$

for all  $i,j \le n$  (6.2)

From (6.2) we infer immediately the equation  $TRes_1(\alpha_1,\alpha_6) = Res_2(\alpha_1,\alpha_6)T$  which applied to (6.1) results

$$\operatorname{Res}_{1}(\alpha_{1}, \alpha_{6}) = \begin{bmatrix} a := t(q*d) - 2*0vf(q*d) \\ i := 0 \\ q_{24} := 0 \\ z := 0vf(q*d) \end{bmatrix}$$

(6.3)

This equation says that the original microprogram  $\Pi_1$  always terminates ((6.3) implies that  $\operatorname{Res}_1(\alpha_1,\alpha_6)$  is a total function) and that it produces the 24-bit representation of the required product. This representation can happen to be modified by an overflow in which case the value of z will become 1 (if q = d = -1, then z = 1 & a = -1).

The final remarks are the following. This method:

-is different from the regular expression method,

-permits the structuring of analyzed programs,

-applies in exactly the same way to programs where

the number of iterations in their loops depends

on the input data,

-may be automated using simple symbol-manipulation

programs.

### REFERENCES

- [1] J.W. de Bakker and W.P. de Roever, A Calculus for recursive program schemes, in <u>Automata Languages</u> and <u>Programming</u> (M. Nivat, ed.) pp.167-196, North Holland, Amsterdam, 1973.

- [2] A. Birman, On proving correctness of microprograms, <u>IBM J. Res. Develop.</u>, vol.18, pp.250-266, May 1974.

- [3] A. Blikle, Iterative systems; an algebraic approach, <u>Bull. Acad. Polon. Sci., Ser. Sci.</u> Math. Astronom. Phys., pp.51-55, vol.20, 1972.

- [4] A. Blikle, Complex iterative systems, ibid., pp.57-61, vol.20. 1972.

- [5] A. Blikle, Proving programs by δ-relations, in Formalization of Semantics of Programming Languages and Writing of Compilers (Proc. Symp. Frankfurt am Oder 1974), Electronische Informationsverarbeitung und Kybernetik (to appear in 1976).

- [6] A. Blikle and S. Budkowski, A general programverification method applied to microprograms, a short paper in Proc. of the 1976 Int. Conf. on Fault-Tolerant Computing (FTCS-6) Pittsburgh, 1976.

- [7] A. Blikle and S. Budkowski, An algebraic program verification method applied to microprograms, Res. Rep. CS-76-31 Dept. of Comp. Sci., Univ. of Waterloo, Waterloo Ontario, Canada N2L 3G1, June 1976.

- [8] A. Blikle and A. Mazurkiewicz, An algebraic approach to the theory of programs, algorithms, languages and recursiveness, in Mathematical Foundations of Computer Science (Proc. Symp. Warsaw-Jablonna 1972) Warsaw, 1972.

- [9] W.C. Carter, W.H. Joyner and G.B. Leeman, Automated experiments in validating microprograms, Digest of Papers of The 1975 Int. Conf. on Fault-Tolerant Computing (FTCS-5), p.247, Paris, 1975.

- [10] T. Ito, A theory of formal microprograms, in Proc. of the Int. Adv. Sum. Inst. on Microprogramming, 1971.

- [11] G.B. Leeman, Some problems in certifying microprograms, <u>IEEE Trans. on Comp.</u>, vol.C-24, No.5, pp.545-553, May 1975.

- [12] G.B. Leeman, W.C. Carter and A. Birman, Some techniques for microprogram validation, Inf. Processing 74, pp.76-80, North Holland 1974.

- [13] Z. Manna, Mathematical Theory of Computation, McGraw-Hill Book Co., New York, 1974.

- [14] A. Mazurkiewicz, Proving algorithms by tail functions, <u>Inf. Cont.</u>, vol.18, pp.220-226, 1971.

- [15] R. Milner, An algebraic definition of simulation between programs, 2nd Int. Joint Conf. Artificial Intelligence, London 1971, pp.481-489.

- [16] D. Paterson, The design of a system for the synthesis of correct microprograms, Micro-8 Proc., Eighth Annual Workshop on Microprogramming, Chicago, Sept.1975.

# MICROPROGRAMMED IMPLEMENTATION OF A SCHEDULER

R. Chattergy University of Hawaii Honolulu, Hawaii

Application of microprogramming to enhance the performance of operating systems has been discussed in the literature in the past [7,1,5]. Two examples of such applications can be found in [4,6]. This paper discusses the philosophy behind the microprogrammed implementation of a scheduler, used in a large, time-shared computer incorporating several processors.

### INTRODUCTION

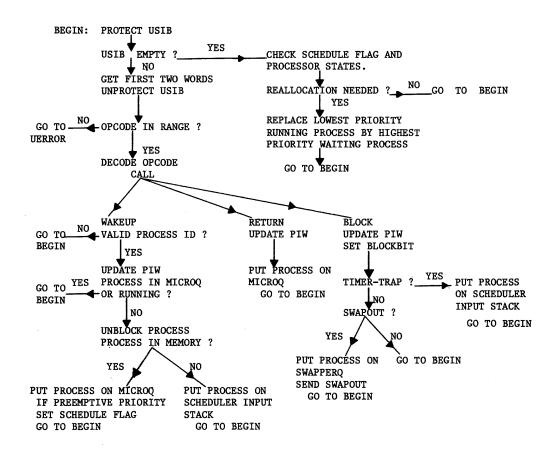

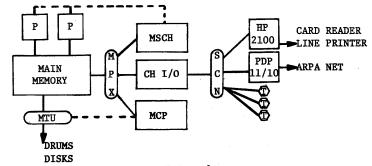

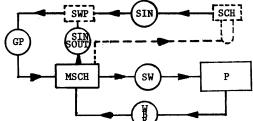

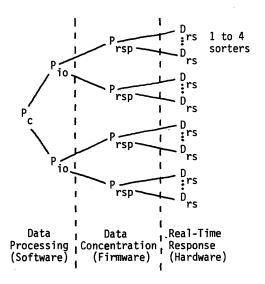

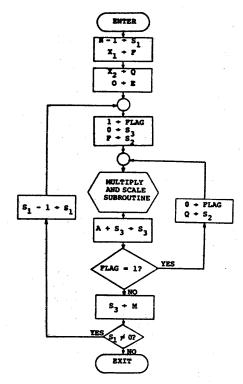

This paper describes the activities of a typical microprogrammed scheduler (microscheduler) in a time-shared system with multiple processors. This description is a simplified version of the actual microscheduler in the BCC 500 computer system, designed by W. Lichtenberger, M. Pirtle, B. Lampson, J. Freeman, R. Schultz and R. Van Tuyl in 1969. A functional diagram of the system is shown in figure 1. The general philosophy of scheduling for a multiprocessing system has been discussed at length in [3]. As mentioned in [3], scheduling consists of two activities. The first is the determination of an optimal schedule based on some scheduling criterion. The second is the enforcement of that schedule on the processes in the system.

Clearly the task of selecting a scheduling criterion and determining a schedule by some algorithm is a complex and evolutionary process. The environment within which resources are allocated by scheduling often changes, forcing a change of the scheduling criterion, and in extreme cases a change of the corresponding algorithm. Hence a scheduling algorithm is unsuitable for microprogrammed implementation in a read-only memory. On the other hand, the task of enforcing a schedule, classified as a midiprimitive in [7], consists of more permanent subtasks such as, the creation and maintenance of queues, blocking and awakening of active processes, making calls on the swapper etc. These subtasks are discussed in detail in the later sections. These subtasks are even system independent in the sense that, they must be carried out in one form or another regardless of the system architecture.

The above considerations prompted the design of the scheduler in the following form. The scheduler is

a hardware processor, microprogrammed to execute a set of instructions in a loop. The task of schedule enforcement is directly microprogrammed as part of this loop. Besides schedule enforcement, the processor also executes a machine instruction of an emulated machine in every iteration of the loop. The scheduling algorithm is implemented in software on this emulated machine. Thus the microscheduler carries out both scheduling activities, executing the scheduling algorithm written in a high-level language for flexibility, and enforcing the schedule discipline via firmware for speed of execution.

### 2. HARDWARE DESCRIPTION

The BCC 500 shown in figure 1, is a large time-shared computer with two processors for executing user-processes, and three special purpose processors for carrying out system management tasks (i.e., executing the operating system). All of the processors operate independently, communicate with each other via main memory, and are microprogrammed. Figure 2 shows the arithmetic-logic unit of a microprogrammed special purpose processor and its bus structure.

All registers shown in figure 2 are twenty four bits wide. M,Q, and Z are the main registers, where M serves as the communication register with the main memory via the main memory interface. The outputs of M and Q are connected to the left Boolbox (LB), and the outputs of Q and Z go into the right Boolbox. Each Boolbox can perform any of sixteen boolean operations on its inputs. The outputs of the Boolboxes are connected to the Adder. The output of the left Boolbox goes into the Cycler.

The outputs of the Adder and the Cycler can be put

into any of the seven Holding Registers, R0,...,R6. The register R0 acts as the memory address register (MAR) when main memory is accessed. The output of any of the Holding Registers can be incremented by one and hence any of these registers can be used as a counter. In addition there are sixty four Scratch Pad registers which are loaded from the X-bus and read onto the Y-bus.

The Control Memory of the microprocessor is a readonly, diode memory containing atmost 2 048, nintybit words. Different fields of the 90 bit microword control different logic circuits and in case of a branch to a subroutine, the return address is automatically stored in an auxilliary register.

### MICROWORD

The bits and fields in the 90 bit words in the control memory are coded to generate the controlling signals necessary to operate the ALU. For example, bits 0-5 are used to set up one of a number of branch conditions to be tested for branching. The bits 8-17 are used to provide the branch address, which can also be obtained from the OS register (return from a subroutine) or the X-bus (computed go to). The bits 18-41 are used to specify a 24-bit constant which can be gated onto the X or the Y buses respectively. A detailed description of all the fields is too long. The above description should be enough to give the reader a "feel" for the system.

### 4. MICRO LANGUAGE

A special purpose readable reference language, called MICRO, is available for writing microprograms for the processors of the BCC 500. The MICRO language has declaration statements and statements for execution. The declaration statements can be used to define macros, give symbolic names to registers, define parameter values, define branch conditions for repeated use in the program, etc. The set of statements for execution consists of the usual assignment (including multiple) statement, memory operations statement, branch instructions, microword-field assignment statements, etc. It is impossible to discuss the language in detail here. Instead, explanatory comments enclosed between "/\*" and "\*/" are imbedded in the sample microprograms provided in the later sections.

### 5. MICROSCHEDULER INTERFACE

A simplified diagram of the interfaces among the system resources and the microscheduler is given in figure 3. In this figure, the microscheduler and the user processors are hardware processors, whereas the swapper and the scheduler are software packages run on the system processors. All processors in the system make WAKEUP calls to the microscheduler to activate processes. If a process, which has received a wakeup call, is not in the main memory, the microscheduler inserts the identity of this process into the input stack of the scheduler. The scheduler, using its scheduling algorithm, assigns a priority to the process which cannot be changed by the other processors. It puts the process in its appropriate position in a queue and makes a SWAPIN call to the swapper. In some cases such as a page-fault condition, the microscheduler can make a direct SWAPIN call to the swapper. Due to lack of adequate memory space, the swapper may fail to

swap in a process. It then makes a GIVEUP call to the microscheduler, asking for the identity of a process that may be swapped out to make room. The microscheduler answers this call via a SWAPOUT call indicating the process that can be swapped out.

The microscheduler alters the work schedules of the processors by making SWITCH calls. A switch call contains the identity of the process to be worked on by the receiving processor. If a new process of preemptive priority preempts the current process on a processor, this information is sent back to the microscheduler via a RETURN call by the processor. If a running process blocks itself, the corresponding processor makes a BLOCK call to the microscheduler. The processor informs the microscheduler whether or not the blocked process should be swapped out (a policy decision made by the monitor).

All communications with the microscheduler are carried out via a stack in the main memory under suitable PROTECT and UNPROTECT mechanisms.

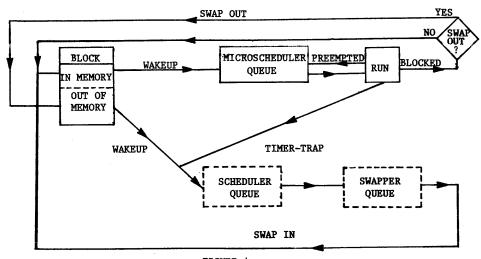

# 6. LIFE-CYCLE OF AN ACTIVE PROCESS

Figure 4 shows the life-cycle of an active process under control of the microscheduler. Consider an active process which receives a call from some other running process. The call is entered under protection into the top two words of the input stack of the microscheduler. The microscheduler periodically inspects the stack for calls from the outside. Upon finding such a call, the microscheduler checks the identity of the process for validity. If the identity is invalid, it ignores the call and delets the entry. For a valid call, the microscheduler determines whether the call is for a wakeup or block.

WAKEUP CALL: The microscheduler merges the data word from the call into the program interrupt word of the process (PIW), stored in the process resident table. It checks to see if the process is either waiting in the microscheduler queue for a processor, or already running. In either case, nothing more needs to be done. For an interesting example of this situation see [2] pp. 271.

On the other hand, if the process is blocked, the microscheduler unblocks the process. It checks to see if the process is in the main memory. If the process is in the main memory, the microscheduler inserts it, according to it's priority, in a queue of processes waiting for processors. Note that if the inserted process has preemptive priority then it can preempt a running process. This means that the microscheduler may have to reallocate the processors. A preemptive priority structure is necessary because the system does not have a hard-wired interrupt mechanism. Preemptive priorities must be assigned to processes whose non-execution can lead to loss of information.

If the process is not in the main memory, it has to be swapped in. The microscheduler then puts the process in a stack of processes waiting for the scheduler. The scheduler determines the priorities of the processes independently, and inserts them in the input queue of the swapper. In some cases, the microscheduler may make a direct request for a

swapin to the swapper.

BLOCK CALL: Whenever a running process blocks, the monitor is activated. The monitor decides whether the blocked process should remain in main memory (page-fault) or be swapped out (input from terminal). This decision is passed onto the microscheduler via the block call. The microscheduler blocks the process and if so directed makes a swapout call to the swapper.

If a process is caught in a timer-trap, the microscheduler does not block it but puts it on the input stack of the scheduler for future scheduling. The scheduler changes the priority of such a process based on its scheduling criterion and sends a wakeup.

RETURN CALL: Whenever a running process is preempted of it's processor by a process with preemptive priority, the processor sends a return call to the microscheduler. The microscheduler removes the process from the run state and puts it in the microscheduler queue to wait for a processor.

### PROCESSOR SCHEDULING

The microscheduler periodically checks the status of each processor and reallocates those processors which are either idle or can be preempted. The processors are directed to switch processes by means of the SWITCH call sent by the microscheduler. In principle, the SWITCH call provides the processor the identity of the new process to be

A processor has three possible states. It is either idle, or running a process, or running a process which has preempted another process. If the processor is in the last mentioned state, then the microscheduler does not send it a switch call untill the process running on it blocks. A processor is switched only if it is idle or running a process which has not preempted another process.

Whenever the microscheduler enters a new process in its queue that has a preemptive priority, it sets up a schedule flag. This flag indicates that reallocation of the processors is necessary. When the microprocessor decides to reallocate the processors, it switches the highest priority process in the microscheduler queue with a process that has blocked.

# 8. MICROSCHEDULER INPUT STACK

Calls to the microscheduler are placed on a stack called USIB in the microprogram. Each call consists of two words. The leftmost six bits of the first word contains an opcode identifying the call, such as 1 for wakeup, 2 for block etc. The rightmost eighteen bits of the first word contains a pointer to the first word of a process's process resident table (in effect identifies the process). The second word contains the bits to be set by the microscheduler in the process interrupt word in the resident table, as a result of the call.

# 9. MICROPROGRAM FOR MANAGEMENT OF USIB

```

USIBIGIN: PROTECT (USIB):

/* Protects stack from use by other processors...*/

MAR + USIBTOP, FETCH;

/* Get pointer to top of stack.....*/

Q + SK7 + M, MAR + USIBASE, FETCH;

/* Get pointer to the bottom of stack.....*/

M EOR Q, GO TO EMPTY IF LB=0, Z+LUSIBE

/* Compare top and bottom pointers stored in M \, */

/* and Q by exclusive OR. If pointers same, out-*/

/* put of left boolbox LB=0. Branch to block

/* labelled EMPTY. LUSIBE=No. of words in call..*/

MAR \leftarrow SK7, FETCH, Z \leftarrow Q-Z;

/* Get first word from stack.....*/

SK7 \leftarrow Q \leftarrow M, MAR \leftarrow MAR+1, FETCH;

/* Get second word from stack.....*/

R2 \leftarrow M;

/* Put second word in register R2.....*/

M ← Z, MAR ← USIBTOP, STORE;

/* Move pointer to top of stack down by LUSIBE */

/* words.....*/

UNPROTECT (USIB);

/* Unprotect stack. The first word fetched from */

/\star stack is in SK7 and Q. The second word is in \star/

/* register R2.....*/

M \leftarrow Q LCY 4, Q \leftarrow 600 000 17B;

M + M AND Q LCY 2, CALL UERROR IF LB=0;

/* Left cycling the contents of Q through M mask-*/

/* ed by 600 000 017 and the last AND operation */

/* leaves the opcode for the microscheduler in

/* the rightmost bits of M. For a valid opcode */

/* this must be > 0. UERROR subroutine is called*/

/* otherwise.....*/

Q \leftarrow MAXOP;

/* Maximum value of opcode is loaded in Q......*/

CALL UERROR ON Q-M < 0. Q \leftarrow OPTAB-1;

/* Call UERROR if the opcode exceeds its maximum */

/* allowable value.....*/

R5 \leftarrow M+Q, Q \leftarrow R2, DGO TO USIBIGIN;

/* R5 stores the pointer to the subroutine (wake-*/

/* up, block etc.) to be used by the microschedu-*/

/* ler as a result of this call. The subroutine */

/* is called in the next line. Q and R2 contains*//* the second word of the call. DGO TO is a de- ^*/

/* layed branch. The branch is executed after */

/* execution of the next instruction is complete.*/

MAR \leftarrow Z \leftarrow M \leftarrow SK7, CALL STKLK, C \leftarrow 3, TCX, TCW;

/* STKLK causes a branch to the subroutine point-*/

/* ed at by R5. It also saves the return address*/

/* in a stack. Because of the delayed GO TO in */

/* the previous line, this return address is that*/

/* of USIBIGIN. Thus a return is made to USIBI- */

/* GIN after a subroutine such as block or wake- */

/* up has been executed. MAR contains the ad- */

/* dress of the PRT plus 3 (ie. the address of *//* the PIW), where the 3 is merged from the con- */

/* stant field of the microword by TCX and TCW...*/

OPTAB: GO TO WAKEUP;

GO TO BLOCK;

GO TO BLOCKOUT;

GO TO GIVEUP;

```

### 10. FLOW-CHART OF THE MICROSCHEDULER

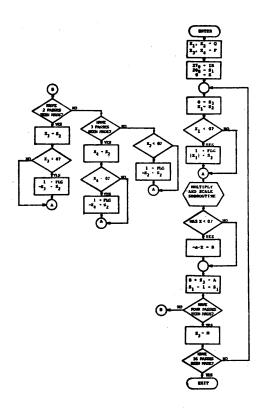

A complete description of all the microprograms is too long to be included in this paper. A flowchart describing the operation of a simple microscheduler is given below.

In the flow-chart, the usual housekeeping operations have been left out. Also the flow-chart does not include such operations as the management of real-time queues, which a microscheduler of a time-shared system must handle. A real-time queue is a queue of processes whose wakeup signals are specified by a real-time clock, and does not come from other processes. Basically, the microscheduler inspects its input stack periodically, and in response to calls left there by other processors it executes proper subroutines such as WAKEUP or BLOCK. It also checks the schedule flag and the states of the processors. Whenever necessary, it reallocates the processors and continues to loop around.

### ACKNOWLEDGMENT

The author gratefully acknowledges encouragement and constructive criticism from Professor Wayne Lichtenberger of the department of Electrical Engineering, University of Hawaii.

#### REFERENCES

- [1] W. H. Burkhardt, R. C. Randel, Design of operating systems with micro-programmed implementation, NTIS Report, PB-224-484, September, 1973.

- [2] R. M. Graham, <u>Principles of system program-ming</u>, John Wiley, 1975.

- [3] B. W. Lampson, A scheduling philosophy for multi-processing systems, <u>Communications of the ACM</u>, vol. 11, No. 5, May, 1968.

- [4] B. H. Liskov, The design of the Venus operating system, <u>Communications of the ACM</u> vol. 15, No. 3, March, 1972.

- [5] J. V. Sell, Microprogramming in an integrated hardware/software system, <u>Computer Design</u>, vol. 14, No. 1, January, 1975.

- [6] W. G. Sitton, L. L. Wear, A virtual memory system for the Hewlett-Packard 2100A, preprints of the seventh annual Workshop on Microprogramming, ACM, September, 1974.

- [7] A. H. Werkheiser, Microprogrammed operating systems, preprints of the third annual Workshop on Microprogramming, ACM, October, 1970.

P - User Processor MSCH - Microscheduler

CH I/O - Character I/O Processor

MCP - Memory Control Processor MTU - Memory Transfer Unit

MPX - Multiplexer SCN - Scanner

T - Terminal

FIGURE 1

MR - M Register

QR - Q Register ZR - Z Register

MMI - Main Memory Interface SCPD - Scratch Pad

SWP - Swapper

SCH - Scheduler

SIN - Swap In

SOUT - Swap Out GP - Giveup

SW - Switch

W - Wakeup B - Block

R - Return

FIGURE 3

FIGURE 4

### AN INSIGHT INTO PDP-11 EMULATION+

J. C. Demco T. A. Marsland

Department of Computing Science University of Alberta Edmonton, Alberta Canada T6G 2H1

In order to evaluate the Nanodata QM-1 as a universal host computer, an emulator for a contemporary computer, the PDP-11, was designed and constructed. It was required that the emulator be functionally equivalent to the target, without making excessive sacrifices in emulation speed. Some properties of emulation hardware necessary to achieve these goals are identified. In addition, the paper describes a monitor designed to support different emulators concurrently on a single host machine.

### 1. INTRODUCTION

Through the design and construction of an emulator for the DEC PDP-11/10 computer [1], the extent to which the Nanodata QM-1 [2, 3, 4] can serve as a universal host is being explored. The results summarized in this paper [5] identify some desirable properties of emulation hardware and show that complete emulation is possible without excessive sacrifices in emulation speed. One primary goal was that the emulator should execute all of the software for the target machine, rather than some specific package.

Many other computer emulations have either been for cutdated machines with long memory access times, simple instruction formats and limited I/O capabilities [6] [7], or have not simulated I/O instructions exactly, but simply translated them into high-level requests to the host machine's operating system [8] [9]. In contrast, the study reported here considers the emulation of a contemporary computer, one with several instruction formats, addressing modes, and a main memory cycle time comparable to that of the host machine (fig. 1).

### 2. THE EMULATOR

With the QM-1, two distinct construction approaches are possible:

Design a special microinstruction set, and implement it in nanocode. The emulator may now be built rapidly as a collection of microprograms.

\*This study was supported by the National Pesearch Council of Canada, Grant A7902.

Implement the emulator's instruction set completely in nanocode; This is referred to as <u>direct</u> emulation, and should provide faster execution.

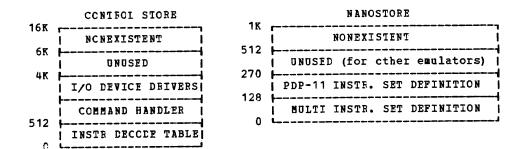

Our emulator is essentially a direct one. Control store is used to hold tables for instruction decoding, a condition code bit map, and microroutines (written in the MULTI [10] instruction set) to handle I/O and control functions. These device drivers make the host peripherals serve the emulator as their target counterparts.

|                                                            | Host<br>QM-1                   | Target<br>PDP-11                            |

|------------------------------------------------------------|--------------------------------|---------------------------------------------|

| REGISTERS   general purpose     special purpose            | 12 6-bit<br>32 18-bit          | 8 16-bit<br>  device regs<br>  (variable #) |

| MAIN STCRE<br>  width<br>  maximum size<br>  cycle time    | 18 bits<br>256K<br>960 nsec    | 16 bits<br>28K<br>980 nsec                  |

| CONTRCI SICRE<br>  width<br>  maximum size<br>  cycle time | 18 tits<br>  16K<br>  160 nsec |                                             |

| NANOSTORE<br>  width<br>  maximum size<br>  cycle time     | 360 bits<br>1K<br>160 nsec     |                                             |

Fig. 1 Properties of User-Accessible Memory

Naturally the microroutines themselves are driven by nanocode, but speed in processing the I/O is of lesser consequence.

For each main store instruction, the high order nine bits of a PDP-11 word are used as an index into one of the control store tables. Fach entry has two fields. The first is typically the nanoaddress of a setup routine, whose purpose is to prepare source and destination values. The second usually addresses an execute routine, which carries out the desired calculation. If an I/O device register is accessed during instruction execution, control is passed to a microroutine to initiate the I/C, before the execution of the next instruction.

# 2.1 <u>Instruction Flow and Routine</u> <u>Descriptions</u>

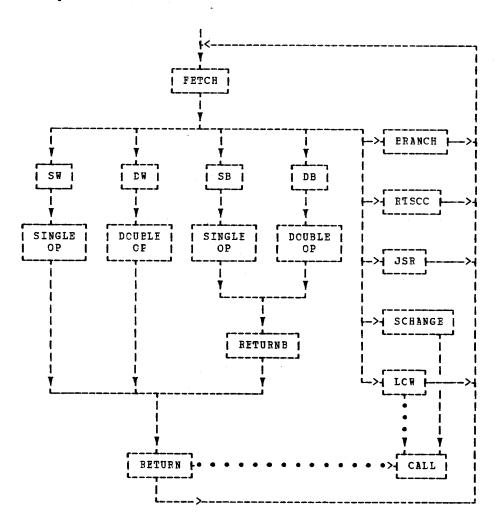

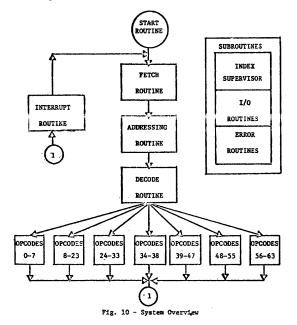

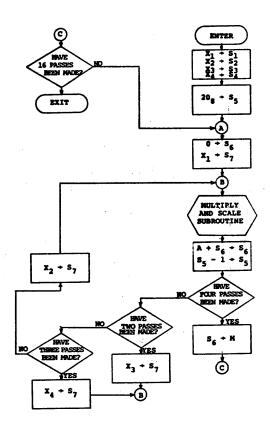

Fig. 2 is a block diagram showing the basic flow as the emulator executes PDP-11 instructions. The multi-way branch after the instruction <u>FETCH</u> routine reflects the execution of one of the setup routines mentioned in the previous section. The

boxes labeled <u>SINGLE OP</u> and <u>DCUBLE CF</u> indicate the use of one of the execute routines. The dotted lines represent conditional invocation of <u>CALL</u>, whose function is to pass control to a microroutine to handle the I/O, plus the HALT, WAIT, and RESET instructions. A summary of each nanoroutine follows:

### • FETCH

Fetches the next instruction from main store and begins decoding it via a setup routine,

### · MODE

A subroutine which calculates the effective address of a PDP-11 instruction operand, and returns its value. MODE is not shown in fig. 2 because it is called from many places. Error checking is performed, with control conditionally passed to SCHANGE,

### SCHANGE

The state-change routine is used to perform TRAP, EMT, BPT, and ICT instructions; it also handles I/O traps and error traps.

Fig. 2 Basic Flow of Control in the Emulator

- · CAII The invocation of microsubroutines to handle I/O, HALT, RESET, WAIT, and logical interrupts is made by this routine.

- Handles the group of instructions in the range 0002XX-0003XX.

- Instructions in the range 6000XX 0001XX are the responsibility of ICW.

- RETURNB Re-constructs a word after a byte operation.

- RETURN Places the result in the location specified by the DST field. If a device word was either read or written during the instruction execution, control passes to CALL otherwise, control passes to FETCH.

### 2.2 Memory Mapping and Utilization

The host memory requirements for each of its three address spaces are summarized in fig. 3. Since the target has a 16-bit word and the host main store word is 18 bits wide, two bits are available as tags. These tags are used to differentiate the target

machine's device registers from the

- remaining existent and non-existent memory.

Bit 17 is 1 if the word does not exist: referencing this location will cause a trap via <u>SCHANGE</u>,

- Bit 16 is 1 if the word is a device register, in which case RETURN will pass control to CALL to perform the I/O function.

The Rotate-Mask-Index (RMI) unit is valuable here for determining the tag settings, but is not essential.

### 2.3 Implementation Shortcomings

Although the emulator successfully executes standard instruction diagnostics, memory and disk exercisers, and also Version 8.08 of the DCS-11 operating system, it does contain some deficiencies as the following details show:

- Odd PC values are ignored; in fact, no PC checking is done at all. The extra time and space required here is probably not justified.

- Stack overflow checking is incomplete for JMF and JSR instructions. Also, the change-of-state routine will not detect stack overflow. Correcting this inaccuracy is almost impossible, given the present structure of the emulator. Elimination of these shortcomings does not

Fig. 3 Memory Allocation in the Host

warrant the excessive space overhead in the nanoprograms. In practice odd PC values should not arise, and stack overflow is detected in a real PDP-11 only after the user's tuffers have been overwritten (fig. 3). In our case, the stack overflow problem stems from the fact that main store is not accessed through a common nanoprogram. The problem is a result of the limited subroutine nesting capabilities within nanostore and means that this emulator cannot be easily extended to handle the PDP-11/45 memory segmentation unit, because a common memory accessing mechanism is essential to deal with address translation,

Finally, the trace trap debugging feature was not implemented. It can be added to the microcode without modification to the nanoprogram portion of the emulator. No need was seen for the feature in our environment, and its implementation offered no new insight into emulation.

# 3. THE EMULATOR CONTROL PROGRAM

Several objectives guide the design of the Emulator Control Program (ECP). First, the control program must not impose architectural restrictions on an emulator, In fact, it should be possible to write an emulator without knowledge of ECP, and then to interface the two easily. Second, provision should be made for the concurrent support of different emulators [11]. Third, member emulators must be given low-level access to I/O devices through ECF and the emulator's device drivers. This is required in order that member emulators can be functionally equivalent to their counterparts, to the point of being able to transport existing software unchanged from the existing computer to the emulator. It was our hope that this approach to I/O handling would also spur thought in such areas as dynamic device ownership, fundamental differences between computer emulators and high-level language emulators, and even the question of whether or not a computer should know how to perform low-level I/O! Finally, basic control and debug facilities must be provided.

The design and implementation of ECP was heavily influenced by a similar system called CONTRCL [12], used by Nanodata Corporation to manage its Nova emulator,

# 3.1 <u>Emulator - ECP Interaction</u>

When the target accesses a device register, control is passed to the ECP. A table of address pairs is searched to match the device register address; the second address is the entry point into the device handler. Also passed to the I/O routine is a read/write flag. This process could occur twice in one main store instruction, if both source and destination are device registers. The device handler responds to

the request by accessing the I/O devices directly. At present, PDP-11 devices [13] which have been implemented include the simulation of an LA30 by a Tektronix 4723 CRT terminal, a PC11 paper tape reader (which is fed information via a Documation-600 card reader!), an IP11 line printer, RK05 disks, and the KW11L line clock.

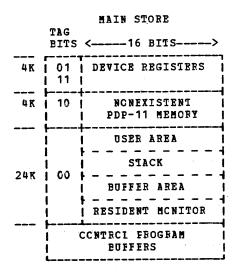

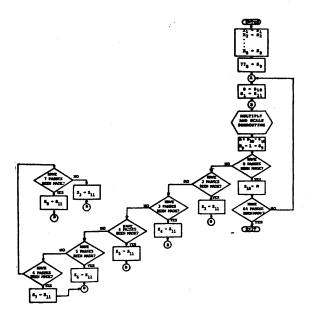

ECP's interrupt handling mechanism has two stages. Interrupts are caught first by the low level handler (with interrupts masked for only a short period), which then places the device's Unit Control Block (UCB) into a priority-ordered queue (fig. 4). A flag is set to signal a logical interrupt, and interrupt processing is completed. When the emulator is restarted, this flag is interrogated by the instruction fetch routine, and control is conditionally passed to the second stage. Once the logical interrupt routine gains control, a

### TASK CCNTROL BLCCK

CM-1 register save area

Iogical halt indicator

Single instr. step indicator

Console command pending

PIP-11 console switches

Iogical wait indicator

Pointer to a priority-ordered

linked list of UCBs needing

service by the upper level

interrupt handler

### UNIT CONTROL BLOCK

| Physical (QM-1) device address| | Lower level I/O handler entry | l address | Device status information 1-----| Link field for queuing the UCB| to the upper level interrupt | handler | Trap vector main store address| 1--------------| Fus request priority **!** - - - - - - - - - - - . . . | Reset routine entry address | 1-----| Device register copies

Fig. 4 FCP Control Block Structure (single emulator environment)

check is made first of the "command pending" word in the Task Control Block (TCB), and if necessary the command handler is invoked. The queue of UCB's is then inspected. If the CPU priority is lower than the bus request priority of the first UCB on the queue, a change of state in the emulator is forced via SCHANGE, Otherwise, the emulator is restarted at the point of interruption.

This bi-level structure has two important features:

- No restrictions are placed on the way interrupts are handled by a member emulator's device drivers. This is especially important if virtual machines with different interrupt structures are to be supported concurrently.

- The handling of an interrupt by a device driver is completely independent of any emulator's software interrupt handler. In particular, loss of an interrupt from a device owned by an emulator which is not currently running does not occur In a system with a small number of terminal devices, it may be desirable to have an emulator console double as the system console. This is easily done by providing a

devices, it may be desirable to have an emulator console double as the system conscle. This is easily done by providing a simple mechanism called conscle redirection to "point" keyboard interrupts at the appropriate handler, either the emulator's or the system's. When the primary console is "cwned" by the emulator, receipt of a special control prefix passes the ownership to the ECP. Commands may then be executed, even while the emulator is active. A command is provided to return console ownership to the emulator. Similarly, more than one emulator may use the same console device.

One of the instructions which the control program has to handle is RESET, which invokes routines to re-initialize the devices that the emulator currently owns. Other obvious problems are for example emulating the HALT instruction, which should not stop the QM-1 (especially in a multi-emulator environment). Similarly the WAIT instruction cannot be dealt with by simply having an interruptible loop in nanocode, since the next interrupt need not necessarily come from a device which the emulator cwns. Rather, WAIT sets the logical wait indicator in the TCB and decrements the PC so that the instruction is re-executed.

# 4. UNIVERSAL HOST EVALUATION